Ingeniero Técnico de Telecomunicación

Electrónica Digital

SISTEMAS ELECTRÓNICOS DIGITALES

17 de Enero de 2000

EXAMEN FINAL

CUESTIONES: (4 PUNTOS)

Describe los procesos de excepción ERROR DE BUS y ERROR DE DIRECCIONES indicando las diferencias entre ambos.

Disponemos de una VIA 6522 y una DUART 68681 y se desea que ambas interrumpan con nivel 4 a un microprocesador MC68000. En caso de que interrumpan simultáneamente se deberá dar prioridad a la VIA. Diseñar el circuito de petición y reconocimiento de interrupción indicando claramente las señales involucradas.

¿En qué consiste un ciclo de Lectura-Modificación-Escritura (instrucción TAS)?. ¿Cuándo se ha de utilizar TAS frente a la instrucción BSET (que genera un ciclo de lectura y otro de escritura normales)?

Enumera las diferentes formas de programación de la velocidad del Transmisor y receptor de la DUART 68681. ¿Que se requiere para poder utilizar las velocidades estándar preprogramadas?. ¿Que significado y ventajas tiene la utilización de un reloj interno 16x?

PROBLEMA: (6 PUNTOS)

Se desea diseñar un sistema electrónico digital con los siguientes componentes:

Un microprocesador MC68000 a 10 MHz.

256 Kbytes de memoria EPROM. Ubicados a partir de la dirección 0 de memoria, en espacio de memoria de programa.

256 Kbytes de memoria RAM, Ubicados a partir de la dirección 0 de memoria, en espacio de memoria de datos.

Dos VIA 6522, con niveles de interrupción 2 y 3 respectivamente, a continuación de la memoria.

Dos DUART 68681, con nivel de interrupción 4 y 5 respectivamente, a continuación de las VIA.

Un convertidor A/D ADC0808, con nivel de interrupción 1, y un convertidor D/A DAC0800 a continuación de las DUART.

Un pulsador que genera una señal de interrupción de nivel 6 (ABORT).

El sistema no necesita de ampliaciones ya que es un sistema definitivo y para realizarlo contamos con los integrados que se muestran en las hojas adjuntadas a este enunciado. Se desea diseñar todo el sistema de manera que la implementación resulte lo más eficiente posible. Para ello tenemos que realizar los siguientes pasos:

Definición del mapa de memoria, indicando que dispositivos responden con /DTACK y cuales con /VPA y las razones. (0.5 punto)

Conexión de las memorias RAM y EPROM. Circuito de decodificación. (1 punto)

Verificación temporal en lectura y escritura de las memorias RAM y EPROM. Diseño del circuito de generación de estados de espera si fuese necesario. (1.5 puntos)

Conexión de los convertidores A/D y D/A al microprocesador. (1 punto)

Conexión de una de las VIAs al microprocesador y una de las DUART. (1 punto)

Diseño total del circuito de petición y reconocimiento de interrupción de todo el sistema, así como la ecuación resultante de las señales /VPA y /DTACK. (1 punto)

Esta es la puntuación del ejercicio propuesto lo que no indica que se tenga que hacer en este orden ni que se pueda hacer en conjunto. Se recomienda hacer uso de ecuaciones antes de poner los esquemáticos de los circuitos y realizar todos los comentarios necesarios para la correcta interpretación de la resolución.

SOLUCIÓN:

APARTADO 1:

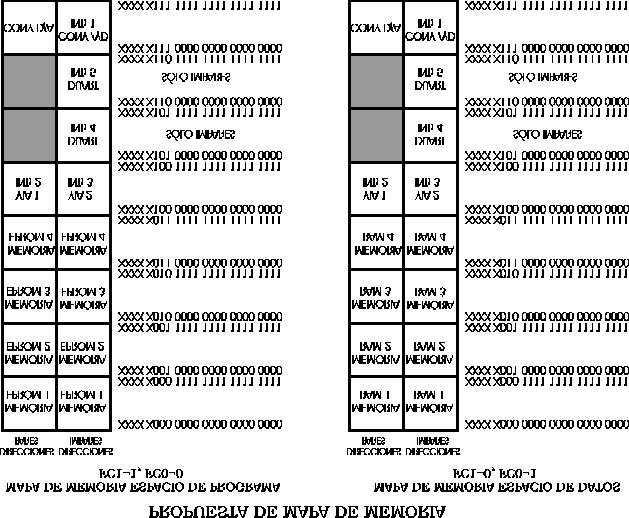

La definición del mapa de memoria del sistema global, la tenemos que hacer de forma que a la hora de la decodificación consumamos los menos recursos posibles. Esto quiere decir que debemos incidir lo más que podamos en la parcialidad de esta decodificación.

El bloque mínimo vendrá marcado por la memoria. Disponemos de circuitos integrados de 32k x 8 con lo que dada la estructura del 68000 el bloque será de 64kbytes (32k para posiciones pares y 32k para impares). La forma más eficiente de realizar este mapa de memoria será la mostrada en la figura, teniendo en cuenta que tenemos dos espacios distintos de memoria: Un primer espacio de direccionamiento (espacio de programa), donde se ubicará la memoria EPROM, y un segundo espacio de direccionamiento (espacio de datos) donde se ubicará la memoria RAM. Esto hará que para la decodificación de la memoria tengamos que incluir las líneas FCx.

Los dispositivos que responden con /DTACK son los dispositivos de memoria o los que se direccionan como tales, siempre y cuando el tiempo de acceso de los mismos nos lo aconseje. Por supuesto dispositivos de la familia del 68000 como la DUART deben responder con /DTACK ya que tienen el pin destinado al efecto.

Es obvio que las EPROM y RAM deben de contestar con /DTACK, así como las VIAs deben contestar con /VPA al tratarse de dispositivos de la familia del 6800. Los convertidores son los que plantean dudas: El convertidor D/A al conectarse a través de un latch o un registro, no es problemático con respecto al tiempo de acceso con lo cual se debe conectar con /DTACK, mientras que el convertidor A/D puede plantear problemas temporales al ser su tiempo de acceso elevado. Si se conecta contestando con /DTACK deberá realizarse el estudio temporal para introducir los estados de espera necesarios, aunque si optamos por conectarlo con /VPA no existirán esos problemas temporales. Este razonamiento se emplea por ser el convertidor A/D un dispositivo de acceso poco frecuente y el introducir un ciclo largo (con /VPA), no influirá en el rendimiento global del sistema

APARTADO 2

A continuación se muestra una propuesta de implementación de la memoria RAM y EPROM que resulta más eficiente en cuanto a elementos utilizados.

Memoria EPROM (Primer bloque)

![]()

Descargar

| Enviado por: | Jose Ramón Ruiz Rodriguez |

| Idioma: | castellano |

| País: | España |