Informática

Microprocesadores modulares

MICROPROCESADORES MODULARES

La modularidad constituye el fundamento de una clase potente de componentes integrados que le permiten a los diseñadores de sistemas especificar su propia y única arquitectura de microprocesador. En esta sección se examina la modularidad y el método de control relacionado de la microprogramación, que se utiliza en la mayoría de los sistemas modulares. Se analiza la serie de microprocesadores modulares 2900 y se aplica al diseño de un microprocesador que emula al 8080.

Modularidad («Bit Slícing»)

Todos los microprocesadores vistos hasta ahora tienen una estructura y un comportamiento perfectamente definido durante el proceso de fabricación. Por ejemplo, los tipos de datos e instrucciones aceptables están cableados en la unidad E de procesamiento de datos y en la unidad 1 de control del programa. Si se han de procesar operaciones o tipos de datos diferentes (por ejemplo, la multiplicación de números en coma fija con longitudes no estándares), entonces se han de simular por software las instrucciones y operandos necesarios. Por supuesto, esto es mucho mas lento que la realización directa por hardware. La velocidad de la mayoría de los microprocesadores está también limitada por su utilización de la tecnología de circuitos MOS, que posibilita una alta densidad de componentes a expensas de trabajar la velocidad de operación con respecto, por ejemplo, a la máxima velocidad de reloj de la CPU permisible. Así pues, las velocidades realmente altas que se pueden conseguir con varias tecnologías TTL y bipolar ECL no están disponibles con generalidad en los microprocesadores estándares. La modularidad resuelve estos problemas proporcionando bloques constructivos flexibles para diseñar microprocesadores que pueden aprovechar las ventajas de las tecnologías de Cl actuales más rápidas.

El dispositivo modular fundamental es un (micro) procesador modular, que es una unidad E de una CPU sencilla con un tamaño pequeño de palabra, típicamente de 4 bits. La propiedad clave de un procesador modular de k bits es el qué se pueden conectar n copias del módulo de una forma regular y simple para formar un procesador de nk bits que realiza las mismas funciones que un único módulo de nk bits en vez de trabajar con operandos de k bits. Los módulos de procesador se interconectan en forma de un circuito cascada o matriz unidimensional. tal como se representa en la figura

Estructura general de un microprocesador modular de nk bits formado por modulos de k bits.

El término «modularidad» proviene de la similitud entre la matriz de procesadores y un microprocesador grande que se hubiese dividido en n subprocesadores idénticos, cada uno operando con un trozo o módulo de k bits del dato que se esté procesando por la matriz. Tal como se indica en la figura, a todos los módulos se conectan las mismas líneas de control, de forma que, en general, todos rea1izan las mismas operaciones al mismo tiempo; estas operaciones son independientes de n, el número de módulos que haya en la matriz de procesadores. Los buses de datos de k bits que transmiten operandos desde o hacia los módulos se unen, simplemente para formar el bús de datos de kn bits de la matriz de procesadores. Conexiones adicionales de datos pueden enlazar módulos adyacentes para permitir la transmisión de las señales de acarreo/adeudo de un módulo a otro durante las operaciones aritméticas.

Es claro que la modularidad permite adaptar el tamaño de palabra de datos de un microprocesador para una aplicación particular. Utilizando seis módulos de 4 bits, por ejemplo, se puede construir un procesador de 24 bits. Es más, un procesador modular se puede particionar dinámicamente de forma fácil en submatrices de diferentes tamaños, lo que simplifica el procesamiento de operandos de diferentes tamaños —palabras de datos de 16 bits y direcciones de 24 .bits, por ejemplo--. Como los módulos individuales corresponden a microprocesadores sencillos sin las unidades I usuales, son lo suficientemente pequeños como para fabricarlos utilizando diseños de circuitos TTL o ECL. Los tamaños de palabra pequeños utilizados para los módulos de los procesadores también hacen más leve otro problema común en microprocesadores, concretamente el disponer de un número limitado de patas en los encapsulados estándares.

Es claro que las operaciones realizadas con un procesador modular deben ser tales que todas las interacciones entre módulos se pueden reducir a una transferencia de señales entre rnódulos adyacentes. En los términos utilizados en el Capítulo 4, los módulos pueden ampliarse mediante la estructura de interconexión de módulos de la figura 8.17. Una revisión de los circuitos MSI y LSI vistos allí muestra que todas las funciones que aparecen en los microprocesadores más simples se pueden realizar con componentes que se pueden ampliar en forma modular. Las instrucciones de transferencia de datos suponen en primer lugar buses de datos y registro paralelo que pueden fácilmente modularse. pues no hay interacción entre bits de datos adyacentes. Los biestables y registros de la serie 7400, respectivamente, muestran de forma clara la estructura modular de la figura anterior

Operaciones booleanas tales como y, o y o-exclusivo, de forma similar, no implican interacciones entre bits de datos adyacentes. y se pueden realizar mediante matrices modulares de puertas (puertas de palabra). Los sumadores con acarreo en cascada constituyen una implantación modular de la suma y de la resta binaria con señales de acarreo/adeudo propagándose de módulo a módulo. Otros ejemplos de dispositivos modulares encontrados anteriormente son los registros de desplazamiento y 105 contadores. Circuitos ALU combinacionales, tal como la ALU de 4 bits 74l81; son módulos procesadores simples capaces de operaciones de transferencia de datos. lógicas, sumas y restas. En la figura 4.27a se tiene una ALU modular de 16 bits formada por cuatro 74181. Los módulos de procesadores considerados en este capitulo son básicamente módulos ALU de este tipo, con la adición de pequeñas RAMs (para archivos de registros) y con los buses de entrada-salida y las funciones de control necesarias para poder manejar un conjunto de instrucciones generales del tipo de las de los microprocesadores.

Para construir una CPU completa es necesario combinar una unidad E modular con una unidad I que pueda captar y decodificar las instrucciones a ejecutar por la unidad E. Normalmente la unidad I de una CPU modular está microprogramada con la organización general que aparece en la figura.

Esquema de un microprocesador modular utilizando control microprogramado

La microprogramación le da al diseñador una flexibilidad en el diseño de unidades I similar a la que proporciona la modularidad en el caso de las unidades E. Las secuencias de control a activar durante la ejecución de las instrucciones se almacenan como listas de microinstrucciones, es decir, microprogramas una memoria especial (usualmente una ROM o PROM) conocida como memoria de control o CM. Frente a esta solución está el control cableado, en el que las secuencias de control producidas por la unidad I se generan utilizando circuitos lógicos secuenciales de propósito especial. Los circuitos lógicos secuenciales de propósito especial. Los circuitos necesarios para captar de CM las microinstrucciones se denominan colectivamente como secuenciadores de microprogramas o controladores de microprogramas. Como se verá próximamente; el concepto de modularidad también se puede aplicar a los secuenciadores de microprogramas.

La primera familia comercial de componentes modulares apareció muy temprano dentro de la evolución de los microprocesadores (Hayes, 1981). En 1973 National Semiconductor introdujo una serie de microprocesadores modulares denominada GPC/P (General Purpose Controller/Processor: Contro1ador/Procesador de propósito general) basado en un módulo procesador de 4 bits denominado R.A.LU (register and arithmetic-logic unit: registro y unidad aritmético-lógica). Fue seguida la serie 3000 de Intel mucho más utilizada, construida con tecnología TTL Shottky más rápida. El módulo procesador 3002 de esta serie se salió de la norma al utilizar palabras de datos de 2 bits. Una de las familias más populares de microprocesadores modulares fue la serie 2900, introducida en 1976 por Advanced Micro Devices (AMD), que, como la serie 3000, utiliza lógica TTL Schottky, pero con módulos procesadores de 4 bits. También hay varias series de microprocesadores modulares ECL incluido el 10800 de Motorola y la serie 100200 de Fairchild; este último es uno de los primeros en incluir un módulo de procesador de 8 bits.

Se muestra a continuación un resumen de las ventajas y desventajas de utilizar microprocesadores modulares a la hora de diseñar.

1. Puede(n) elegirse a la medida el(los) tamaño(s) de palabra(s) del procesador.

2. Utilizando la microprogramación puede diseñarse a la medida el repertorio de instrucciones.

3. Se pueden utilizar tecnologías de CI más rápidas, tales como TTL y ECL.

4. Se requiere un gran número de CIs para formar una CPU completa.

5. Se requiere un coste de desarrollo elevado para el diseño hardware y la microprogramación

El diseñador del sistema puede especificar el(los) tamaño(s) de la(s) palabra(s) del procesador. la composición del repertorio de instrucciones y otras características clave de la arquitectura, y pueden optimizarse para una aplicación particular. Además se pueden utilizar tecnologías de CI más rápidas. que pueden no resultar adecuadas para fabricar microprocesadores no modulares mayores debido a las restricciones en la densidad de componentes de CI, a la disipación de potencia ~ al número de patas. El precio que se paga por este incremento en la flexibilidad y en la velocidad es el mayor número de CIs necesarios para construir una CPU y el incremento sustancial en el esfuerzo total requerido para el diseño. Una desventaja más es que con las computadoras modulares se utiliza un repertorio de instrucciones no estándar, lo que impide utilizar programas estándares fácilmente disponibles.

Los microprocesadores modulares se aplican principalmente en sistemas de propósito especial que requieren velocidades de transferencias de datos o de procesamiento aritmético no usuales. Ejemplos de tales sistemas son los terminales para imágenes gráficas, los sistemas para control de la navegación y computadoras grandes de propósito general. Estas aplicaciones explotan la ventaja con respecto a la velocidad inherente a las familias lógicas de CI más rápidas que se utilizan, así como ala flexibilidad de diseño resultante de la modularidad y de la microprogramación. La ventaja relativa a la velocidad debida a la tecnología de Cl utilizada es de esperar que disminuya conforme las mejoras en la fabricación permitan que estas tecnologías se apliquen a los microprocesadores convencionales no modulares.

Microprogramación

La unidad I, o unidad de control del programa, de una CPU es responsable de la captación de instrucciones de la memoria principal, interpretando sus codops y activando las señales de control que disparan las diferentes etapas requeridas para ejecutar las instrucciones. Debe también responder a las señales de control externas generadas por la unidad E o por los dispositivos de E/S que afecten a la secuencia ejecución de la instrucción. Por ejemplo, las señales (indicadoras) de estado de unidad E influyen en el comportamiento de las instrucciones de ramificación condicional. La ejecución de la instrucción también se modifica mediante peticiones de interrupción y de DMA prevenientes de los dispositiivos de E/S. Dado que usualmente debe tener en cuenta cientos de codops diferentes en lenguaje máquina y un numero comparable de señales de control diferentes, la unidad I es una dé las partes mas complejas de una computadora, y por tanto una de las más difíciles de diseñar.

Se han desarrollado dos soluciones básicas para el diseño de la unidad I: cableado y microprogramación. Las unidades I cableadas utilizan un circuito secuencial fijo para producir las señales de control requeridas: ver la figura a .El diseño de la unidad I se ajusta. en consecuencia, a su repertorio específico de instrucciones, y se puede optimizar con respecto a la velocidad de operación y al çoste del hardware. La información de control asociada con cada instrucción se introduce de forma efectiva en los circuitos lógicos de la unidad I. Las unidades I cableadas tienden a ser interconexiones no estructuradas o al «azar», especialmente cuando se intenta minimizar el número de puertas o transistores utilizados en su diseño. Cambios en el repertorio de instrucciones (por ejemplo, para corregir errores durante el desarrollo de1 diseño) requieren rediseñar total o parcialmente la unidad I. y este es un proceso caro y que lleva tiempo. Dada su complejidad, las unidades I cableadas son particularmente propensas a los errores de diseño. También es difícil rediseñarlas para ampliar el repertorio de instrucciones, requisito común en la evolución de las familias de microprocesadores.

La microprogramación fue definida por Maurice V. Wilkes, de la Universidad de Cambridge, y otros, en los años cincuenta, como una tecnica para hacer más sistemático y más flexible el diseño de la unidad I. En consecuencia, a pesar de su prefijo común, los conceptos de microprogramación y microprocesadores no están relacionados. En la figura b se ilustra la organización típica de una unidad I microprogramable. La información de control se almacena en la forma de microprogramas —secuencias relacionadas de microinstruccjones— en una memoria de control CM. Usualmente hay un microprograma por cada tipo de instrucción, con microinstrucciones adicionales para funciones tales como la captación de instrucción, el cálculo de la dirección de los operandos y el procesamiento de las interrupciones.

Las dos organizaciones principales de la unidad I: a) cableada; b) Microprogramada.

Un microprograma se ejecuta captando de CM las microinstrucciones que lo forman, una a una. Cada microinstrucción se carga en el registro MIR de microinstrucciones, del que se obtienen los correspondientes valores de las señales de control. quizá tras alguna decodificación adicional. El contador de microprogramas MPC actúa como registro de direcciones de CM, incrementándose MPC en uno durante la ejecución de cada microinstrucción, de forma que apunta a la siguiente microinstrucción consecutiva almacenada en CM. La lógica de selección de dirección conectada a MPC permite cargarlo con una dirección de ramificación no consecutiva como respuesta a las condiciones externas. Normalmente la dirección de ramificación se obtiene a partir de un campo de dirección de la microinstrucción situada actualmente en MIR; un campo de selección de condición especifica qué señal externa de entre las posibles se ha de utilizar como condición de ramificación.

Una computadora microprogramada tiene dos niveles distintos de control: el de instrucción y el nivel de microinstrucción.

En el nivel de instrucción la CPU ejecuta continuamente ciclos de instrucción que implican las siguientes etapas:

1. La CPU capta de la memoria principal M una instrucción I cuya dirección está almacenada en el contador del programa, PC.

2. En un registro de instrucción, IR, se coloca la parte de codop; a continuación se decodifica y se ejecuta la operación especificada por IR.

3. PC se modifica para que apunte a la siguiente instrucción a captar de M.

En el nivel más bajo, de microinstrucción, tiene lugar una secuencia similar de operaciones, ejecutando la unidad I ciclos de microinstrucción de forma continua o como sigue:

1. La parte de dirección (secuenciador de microprogramas) de la unidad 1 capta de la memoria de control CM una microinstrucción MI, cuya dirección se almacena en el contador MPC de microprogramas.

2. En el registro MIR de microinstrucciones se carga MI y se decodifica, si es necesario, para producir las señales de control requeridas.

3. MPC se modifica para que apunte a la siguiente microinstrucción a captar de CM.

Un ciclo de microinstrucción se puede ejecutar más rápidamente que un ciclo de instrucción dado que las microinstrucciones se almacenan dentro de la CPU, mientras que las instrucciones han de ser captadas de una memoria externa. Normalmente microinstrucciones también requieren menos decodificación que las instrucciones.

Las acciones controladas por las microinstrucciones toman la forma de ,microoperaciones, que pueden ser realizadas directamente por el hardware disponible. Estas microoperaciones incluyen la carga de registros, la conducción de datos a través de mutiplexores, decodificadores, buses y demás a través de una red, y la selección de funciones a realizar por unidades de multifunción tal como es la ALU. Cada microinstrucción define un conjunto de una o más microoperaciones que se pueden rea1izar conjuntamente en un ciclo de microinstrucción. Por ejemplo, considérese a instrucción de multiplicación binaria de la forma

Z: = Xx Y

Esto se puede ejecutar mediante un circuito de multiplicación, que puede sumar, desplazar, contar, y microoperaciones similares relativamente simples.

Unidades de control microprogramadas

Las instrucciones de maquina se colocan de manera secuencial en el sistema de memoria del procesador, para formar un programa en lenguaje maquina. Estas instrucciones indican al procesador que debe hacer a alto nivel, aunque sólo incluyen las actividades internas requeridas. Un controlador microcodificado usa el mismo concepto de programa almacenado para dirigir en forma interna al procesador conforma ejecuta una instrucción de máquina.

La información que define las acciones requeridas para ejecutar las instrucciones de máquina se almacena como una secuencia de microinstrucciones, microprograma o microcódigo en el controlador.

Las instrucciones de máquina se llaman macroinstrucciones, para distinguirlas de las microinstrucciones. La figura muestra un diseño simplificado para un controlador microprogramado.

Un mapeador extrae del registro de instrucción el código de operación de la macroinstrucción y éste se usa para obtener una dirección la cual es el inicio de una secuencia de microinstrucciones que definen las acciones requeridas para ejecutar la macroinstrucción. Las microinstrucciones se traen de micromemoria al registro de microinstrucciones y se decodifican para generar un conjunto de señales de control.

El controlador genera una secuencia de señales de control sincronizadas, ejecuta una secuencia de microinstrucciones y se sincroniza mediante una señal de reloj externo.

Ejemplo simplificado de un controlador microprogramado

Hay dos maneras de almacenar información de control en las macroinstrucciones: codificación horizontal o vertical. La codificación horizontal usa un bit para representar cada punto de control en el procesador, lo cual es muy flexible y no requiere decodificación, aunque produce microinstrucciones largas. Otra posibilidad es la codificación vertical, donde las combinaciones de señales de control requeridas se comprimen en un código más compacto, lo que ahorra espacio en el almacenamiento de microinstrucciones. No se requieren ciertas combinaciones de señales, lo que hace que se pierda la flexibilidad. En la práctica se usa una combinación de los dos métodos para llegar a una forma de diseño.

Las microinstrucciones contiene otros campos de señales de control los cuales se refieren al flujo de control en el microprograma que se esta ejecutando dentro del controlador.

La figura siguiente muestra el formato se la instrucción de NEMiSyS.

Formato de la microinstrucción de NeMiSyS.

El campo de control de carga indica cómo se debe obtener la localización de la siguiente microinstrucción por ejecutar. Puede ser la siguiente en el almacenamiento de microinstrucciones o estar en la localización dada en el campo de la siguiente instrucción. La selección entre estas dos puede ser condicional y depender del contenido del registro de estado de programa. Si así sucede, los bits que deben probarse se seleccionan por una máscara en el campo de selección de condición. pueden ser condicional.

La capacidad de mapeo usa los campos del código de operación o de modo de direccionamiento en el registro de la instrucción como índice para una tabla de direcciones en el almacenamiento de microinstrucciones. El controlador usa estas direcciones para saltar a las subrutinas de micrócodigo, una para cada microinstrución y modo de direccionamiento.

Secuenciador de microprograma para una memoria de control

Secuenciador del microprograma

Una unidad de control de microprograma debe mirarse como constituida por dos partes: el control de memoria que almacena las micro construcciones y los circuitos asociados que controlan la generación de la dirección siguiente. La parte de generación de dirección es denominada un secuenciador de microprograma, puesto que él secuencia las microinstrucciones en el control de memoria. Un secuenciador de microprograma puede construirse con funciones digitales para satisfacer una aplicación particular. De la misma manera que hay unidades ROM grandes disponibles en paquetes de circuitos integrados, así hay secuenciadores de propósito general adecuados para la construcción de unidades de control de microprograma. Para garantizar un amplio rango de aceptabilidad, un secuenciador de circuito integrado debe proporcionar una organización interna que pueda adaptarse a un amplio rango de aplicaciones. El propósito de un secuenciador se microprograma es presentar una dirección a la memoria de control para que una micro construcción pueda ser y ejecutada. La siguiente dirección lógica del secuenciador determina la fuente de dirección especifica que debe cargarse en el registro de control de dirección. La algunos secuenciadores proporcionan un registro de salida que puede funcionar como el registro de dirección para el control de memoria.

El control d memoria se incluye en el diagrama para mostrar la interacción entre el secuenciador y la memoria asignada a él. Hay dos multiplexores en el circuito. El primer multiplexor selección selección una dirección de una de las cuatro fuentes y las en ruta a un registro de control de dirección CAR. El segundo multiplexor verifica el valor del bit de status seleccionado y el resultado de la prueba es aplicado a un circuito de entrada logica.

La salida del CAR proporciona la dirección para el control de memoria.

El contenido de CAR es incrementado y aplicado a una de las entradas delmultiplexor y al registro de subrutina SBR. Las otras tres entradas al multiplexor número 1 vienen del campo de dirección a ka micro construcción presente, de la salida numero 1 vienen del campo de dirección a la micro construcción presente, de la salida de SBR, y de una externa que mapea la macro-operación , aunque el diagrama muestre un solo registro de subrutina, un secuenciador típico tendrá una pola de registro de alrededor de cuatro a ocho niveles de profundidad.

De esta manera, se pueden activar un numero de subrutinas al mismo tiempo una operación de empujar y vaciar, junto con el indicador de pila, almacenan y retiran la dirección de retorno durante las micro construcciones de llamar y de retornar.

Microprocesador de bit dividido

La CPU de un computador digital puede dividirse en dos unidades funcionales: la unidad procesadora y la unidad de control. Un CPU que es construido con componentes CI tales como unidad procesadora, secuenciador de microprograma, y control de memoria se denomina microprocesador de bit dividido. Este procesador puede diseñarse para proporcionar una arquitectura que se conforma con cualquier especificación. La longitud de palabra puede ajustarse a la aplicación particular y su conjunto de instrucciones puede definirse por medio de un microprograma.

La componente central de un diseño de bit dividido es la unidad procesadora de bit dividido que está organizada eb forma modular típicamente tiene cuatro bits de amplitud.

Una CPU microprogramable de bit dividido tiene el diagrama de bloque funcional básico que se muestra en la siguiente figura.

Figura. Diagrama de bloques de una CPU de bit dividido

La unidad procesadora se construye con componentes CI de 4 bits divididos.

El diagrama muestra una unidad procesadora de 16 bits de ancho formada con cuatro CIs. La estructura interna de una unidad procesadora de 16 bits de ancho formada con cuatro CIs. La estructura interna de una unidad procesadora típica se muestra en la figura 7-1. los bits de estatus en el procesador tales como acarreo, signo, cero, y sobreflujo, son aplicados al secuenciador del microprograma. La función de mapeo convierte los bits del código de instrucción a una dirección de control de memoria.

Cuando el registro de oleoducto insertado entre el control de memoria y el procesador es utilizado proporciona un aislamiento entre la microinstrucción presente la cual se encuentra disponible en la salida del registro y la microinstrucción siguiente que es leída del control de memoria. Mientras la microinstrucción presente está ejecutando las micro-operaciones en el procesador, la dirección siguiente puede leerse del control de memoria.

Todas las componente necesarias para diseñar una CPU de bit dividido se encuentran disponibles en pastillas de circuitos integrados de alta velocidad. Los microprocesadores de bit dividido se diseñan y fabrican para lograr un alto nivel de comportamiento y satisfacer una necesidad específica.

Formatos de microinstrucción

Los bits de una microinstrucción son divididos usualmente en partes denominados campos. Los diversos campos que se encuentran en los formatos de microinstrucción presentan las siguientes funciones:

Una palabra de control que inicia las micro-operaciones en el sistema. Los bits de la palabra de control algunas veces se subdividen en campos separados.

Bits de control y dirección para el secuenciador para especificar la manera en que la dirección de la microinstrucción siguiente debe ser evaluada.

Otros campos especiales contienen datos para transferir u un destino dado.

El proceso de introducir los datos en el sistema de la salida del control de memoria es una técnica frecuentemente utilizada en muchos sistemas microprogramados. El campo en la palabra de control que hace esto es llamado un campo emisor o un campo literal. La salida del campo emisor puede ser utilizada para colocar los registros de control e introducir datos en los registros procesadores.

La familia 2900

Desde su introducción en 1976, la serie de AMD se ha convertido en una de las familias de microprocesadores modulares mas ampliamente utilizadas. Comprende un amplio conjunto de CIs compatibles, todo con el código numérico 2900, para la construcción de microcomputadoras modulares microprogramables. En la serie se utiliza la tecnología TTL Schottky de bajo consumo, que combina una alta velocidad con un moderado consumo. Los miembros de la familia 2900 se pueden agrupar como sigue:

1.- Procesadores modulares

2.- Secuenciadores de microprogramas, algunos de los cuales son modulares.

3.- Memorias (RAMs y PROMs).

4.- Diferentes circuitos SSI y MSI (circuitos para entradas y salidas al bus, decodificadores, registros, etc.)

La serie de CIs estándar 74LS00 también se puede utilizar en los sistemas basados en el 2900. Entre las posibilidades a utilizar en el diseño de software está el lenguaje microensamblador AMDASM, y sistemas de desarrollo de microprocesadores con posibilidades especiales para el diseño y comprobación de microprogramas. Un microprocesador o microcomputadora completa construida con componentes de la serie 2900 es de esperar que tenga 50 o mas CIs. Este elevado numero de componentes queda compensado por el hecho de que se pueden conseguir unas prestaciones significativamente mas altas de lo que es posible con microprocesadores o microcomputadoras con una sola pastilla.

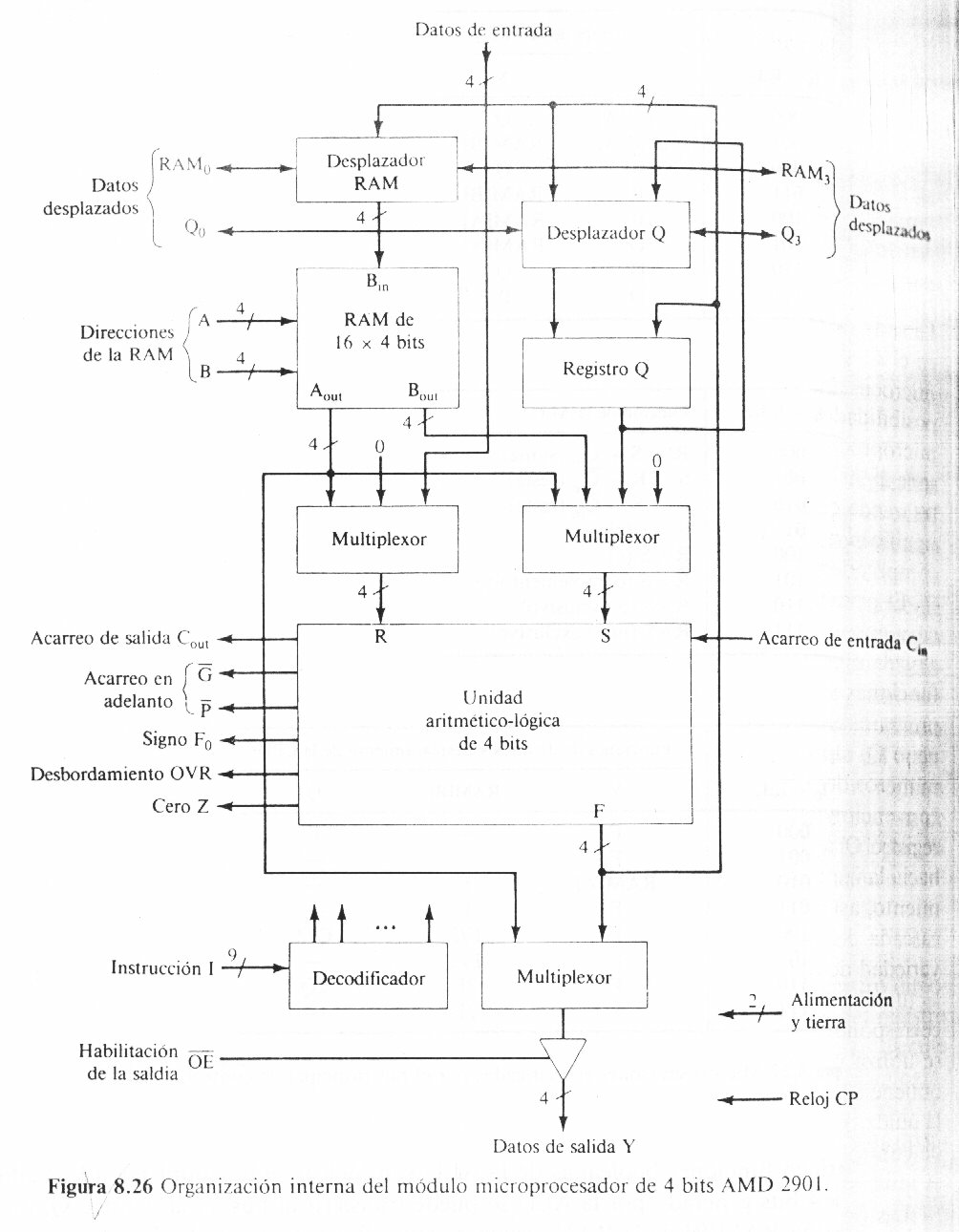

El primer módulo procesador en la serie 2900 es el procesador de 4 bits 2901, cuya organización interna se ilustra en la figura siguiente:

Es una unidad bastante simple alojada en una cápsula de 40 patas. Contiene una ALU combinacional con ocho funciones y una RAM de 16 x 4 bits, que constituye un conjunto de 16 registros programables de propósito general; hay también un registro para resultados denominado Q, similar al acumulador. La ALU puede realizar la suma y la resta con números de 4 bits en complemento a dos, así como algunas operaciones boolenas convencionales. Un par de circuitos desplazadores permiten que el contenido del registro Q y el resultado F de la ALU se desplacen una posición hacia la derecha o hacia la izquierda. La ALU produce indicadores de estado de signo cero y desbordamiento, así como la información de acarreo necesaria tanto para la propagación en cascada del acarreo como para el acarreo en adelanto. La RAM del 2901 es de la variedad de doble puerta, que significa que simultáneamente se pueden realizar dos lecturas. Se le suministran 2 direcciones A y B, y tiene 2 puestas de salida correspondientes, A y B; hay una sola puerta de entrada a la RAM y en este caso se utiliza únicamente la dirección B. Las dos direcciones de 4 bits de la RAM se obtienen a partir de los campos de control de la microinstrucción suministrada para la unidad I controlada, tal como se hace realmente con todas las señales de entrada de control del 2901. Para la transferencia de datos externos hacia o desde el 2901 se utilizan dos buses de 4 bits, D e Y, respectivamente.

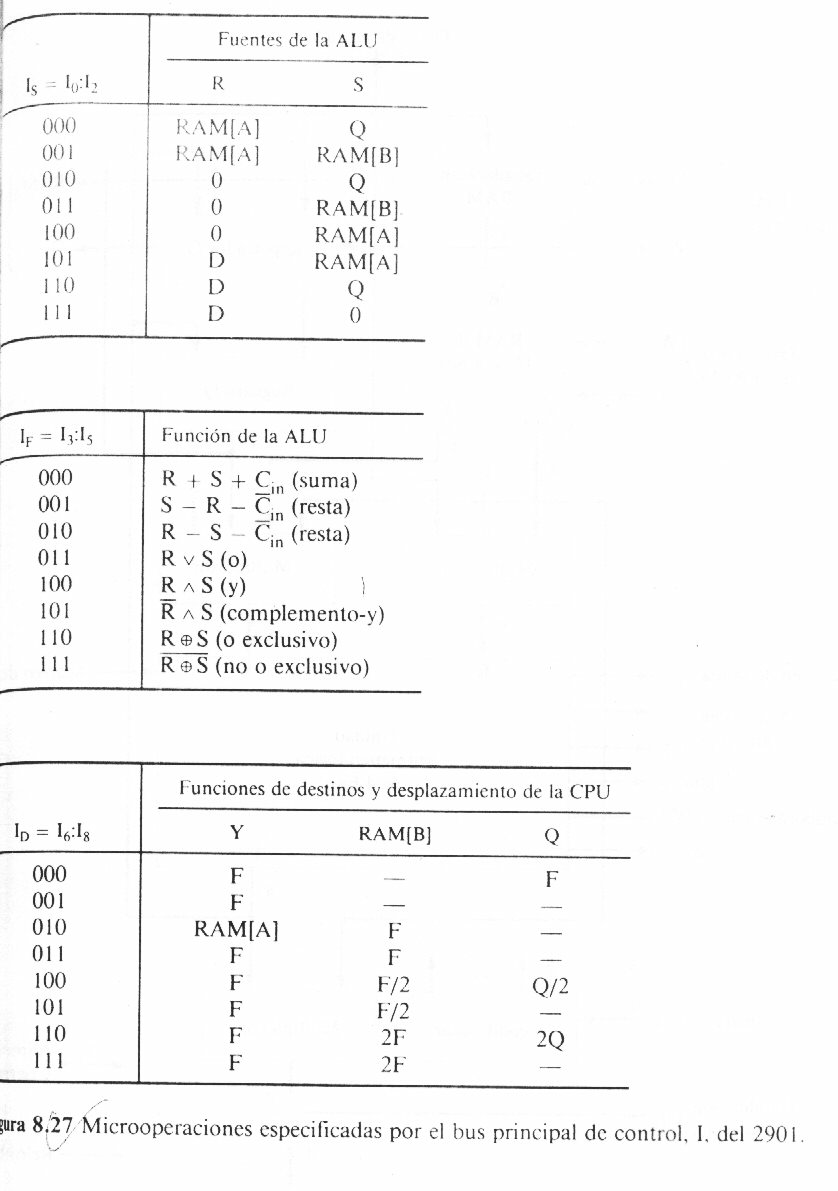

Las (micro)operaciones realizadas por el 2901, y por tanto por una matriz de módulos del 2901, esta determinadas por un bus I (instrucción) de 9 bits. I se subdivide en tres subcampos principales, denominados IS, IF e ID. Con IS se especifican las fuentes de los operandos de entrada R y S de la ALU. Con IF se especifica la función a realizar por la ALU. Finalmente, ID indica el destino del resultado F de la ALU; ID también se utiliza para especificar operaciones de desplazamiento tanto para F como para Q. En la figura siguiente se definen todas las formas posibles de especificar I.

La ALU tiene cinco fuentes diferentes de operandos de entrada, incluidas las posiciones RAM[A] y RAM[B] de la RAM direccionadas mediante los buses de direcciones A y B, el registro Q, el bus de datos D y la constante 0000 (cero). En la figura anterior se dan las ocho combinaciones permitidas para estas fuentes de datos de la ALU. Las funciones de suma y resta de la ALU incluyen Cin como una señal de entrada de acarreo/adeudo para permitir que las operaciones aritméticas se amplíen fácilmente mediante una matriz de módulos del 2901. Es inmediato ver que las cinco funciones booleanas de la ALU son lógicamente completas. El resultado F de 4 bits generado por la ALU se puede transferir al bus Y, al registro Q, o a la posición RAM[B] de la RAM, según se especifique mediante ID. En algunos casos F se desplaza hacia la izquierda o hacia la derecha (representado por la figura anterior por multiplicación y división por dos, respectivamente) al dirigirse a RAM[B]; también se puede realizar un desplazamiento auxiliar con el contenido de Q. Señalemos que el 2901 tiene cuatro líneas de desplazamiento bidireccionales que permiten que las operaciones de desplazamiento se amplíen a través de una matriz de procesadores 2901

El módulo procesador 2903 de 4 bits es una versión mejorada del 2901 que tiene las siguientes prestaciones nuevas. El bus de 4 bits de entrada de datos D se sustituye por un par de buses de 4 bits: un bus de entrada DA y un bus bidireccional de E/S, DB. Además de añadir un nuevo y útil camino de datos al modulo procesador, DB posibilita unir al 2903 CIs externos RAM para incrementar la capacidad efectiva de su archivo de registros RAM internos que, como en el caso del 2901, puede almacenar 16 palabras de 4 bits. El 2903 también tiene un conjunto de funciones aritmético-lógicas especiales, principalmente del tipo suma/resta condicional con desplazamiento, que facilita la microprogramación de la multiplicación, la división y operaciones similares.

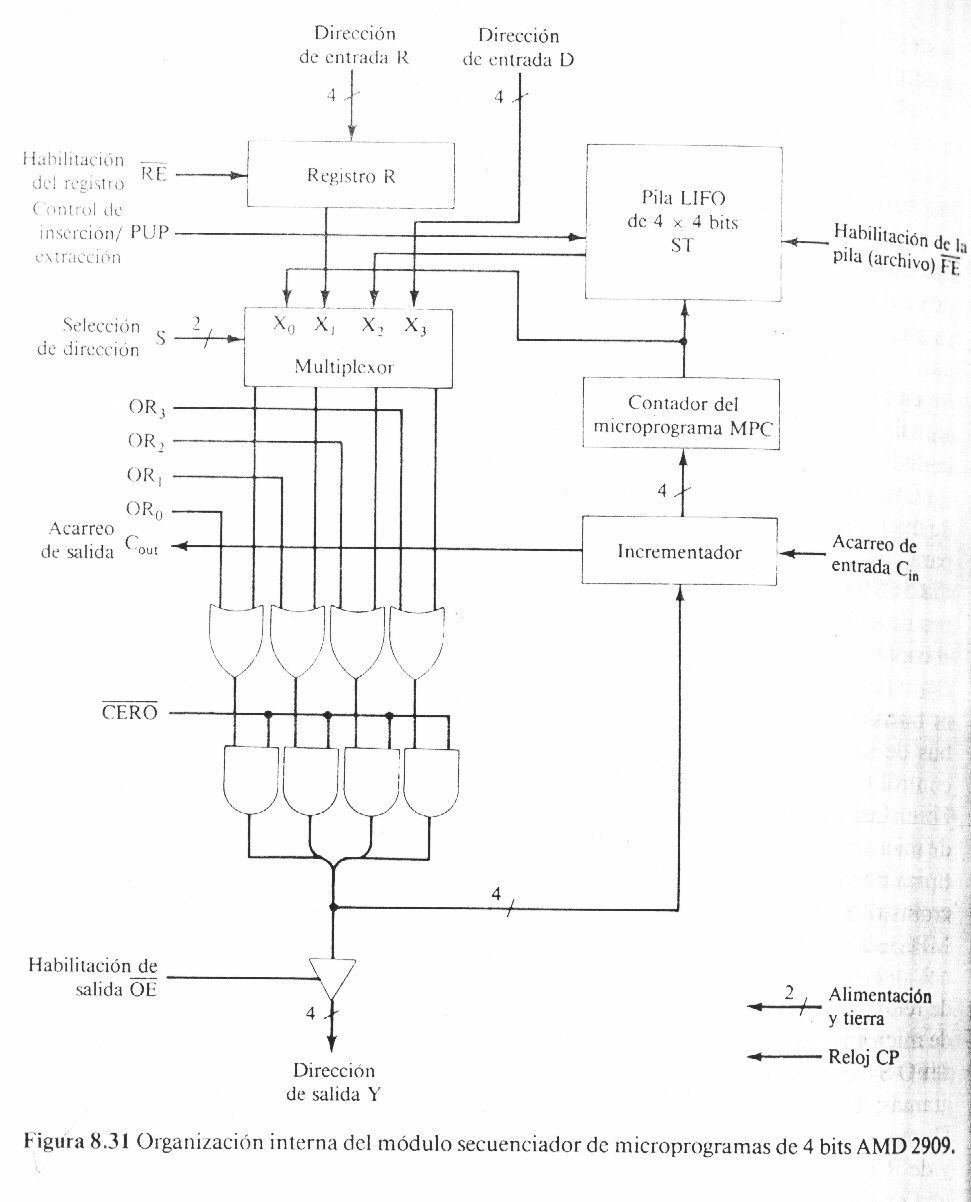

Otra clase importante de componentes de la serie 2900 son los secuenciadores de microprogramas, que generan las direcciones de las microinstrucciones a ejecutar para controlar el comportamiento global de un sistema modular.

El CI 2909 secuenciador de microprogramas esta diseñado para generar las direcciones de 4 bits, pero a su vez es modular, de manera que se pueden unir en cascada n copias del 2909 para formar un secuenciador de microprogramas con 4 n bits. La estructura interna del modulo 2909 aparece en la figura siguiente.

La función del 2909 es transferir una dirección de una de entre varias fuentes internas o externas a su bus de salida Y, que va directamente a la puerta de dirección de la memoria de control CM. El 2909 utiliza cuatro fuentes de dirección: un bus de datos externos, D; un registro R, que esta unido a un segundo bus de datos externo; un contador de microprogramas, MPC; una pequeña pila de cuatro palabras, ST. D y R se utilizan típicamente para canalizar las direcciones de ramificación desde el registro de microconstruccion hacia el secuenciador de microprogramas, y a continuación a CM. MPC esta formado por un registro de 4 bits y un circuito incrementador combinacional, que esta diseñado de manera que MPC recibe la dirección Y+Cin cada ciclo de reloj. La dirección siguiente Y se toma de MPC cuando se ejecuta una secuencia de microinstrucciones almacenadas en posiciones consecutivas de MC. La memoria LIFO ST esta ideada para permitir llamadas y retornos a subrutinas en los microprogramas; desempeña el mismo papel que el registro de subrutinas del 8086. Durante una operación de llamada el contenido actual de MPC se inserta en la pila, y de R o D se obtiene la dirección de la subrutina a la que se llama. Para ejecutar una operación de retorno desde subrutina, de ST se extrae la dirección de retorno y se coloca en el bus Y.

El 2909 contiene un multiplexor con cuatro entradas de 4 bits que selecciona una de entre R, D, MPC, o ST como la siguiente fuente de dirección. Sus dos líneas de selección S se activan, consecuentemente, mediante señales que contienen información sobre la condición de selección, obtenidas a partir de la microinstrucción. MIR.

La serie 2900 también contiene un secuenciador de microprogramas de 12 bits en una sola pastilla, el 2910, que no es modular. El 2910 es bastante similar a la matriz con 2909 de la figura anterior, pero tiene bastantes mejoras. El registro R se puede utilizar como un contador de iteraciones para simplificar la microprogramación de funciones tales como la multiplicación y la división. Las líneas de entrada de selección de condición se organizan en un conjunto de 16 palabras de control, que se pueden condicionar a variables externas o al contador interno R. Esto proporciona, de manera más directa que el 2909, un conjunto de instrucciones de control del microprograma condicionales e incondicionales, incluyendo saltos, llamadas, retornos y bucles.

op

dm

sm

Estado de programa

Incremento

Mapeadores

Selección de carga del multiplexor

Contador del programa

Reloj

Memoria para microcódigo

Selección de condición del MUX

Siguiente instrucción

Cargar Control

Mascara de condición

Control

Decodificador

Señales de control

Microinstrucciones

Registro de instrucciones

Cargar Control

Sig.

instrucción

Máscara Cond.

Activar

bit

Borrar

bit

Incr.

bandera

val

OP

S

D

R/w

ancho

PSR

PC

Const D

ALU

Transferir

S D

Acceso a

memoria

Señales de control

Secuenciador del MIcroprograma

Memoria de Control

Registro de oleoducto

Trozo de 4 bits

Trozos de 4 bits

Trozos de 4 bits

Trozos de 4 bits

Procesador de bit dividido

MAP

externo

Z

S

i

I

MUL 2 de selección

T

I0

I1

Lógica de entrada

S1

S0

MUL 1

3 2 1 0

SBR

Incrementador

CAR

ADF

BR

CD

Micro-ops

Memoria de control

Bus de control

Bus de datos

Modulo procesador S0

Modulo procesador Sn-2

Modulo procesador Sn-1

Registro de instruccion

Secuenciador de microprogramas

(puede ser modulada)

Datos

Memoria de control CM

Dirección

Registro d e microinstruccion

Descargar

| Enviado por: | Wini |

| Idioma: | castellano |

| País: | México |