Electrónica, Electricidad y Sonido

Familias lógicas

LÓGICA EMITTER-COUPLED

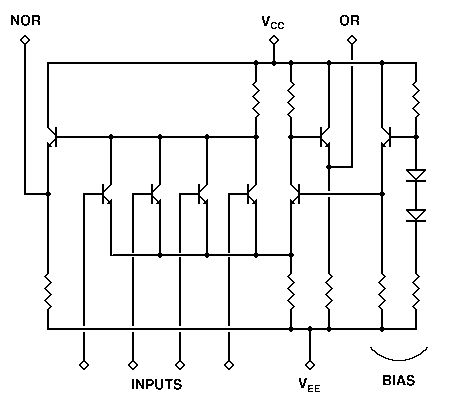

La lógica Emitter Coupled esta basada en el uso de amplificadores diferenciales de múltiples entradas para amplificar y combinar las señales digitales y de seguidores de emisor para ajustar los niveles de voltaje de corriente directa. Como resultado, ninguno de los transistores en la compuerta entra nunca en saturación, así como tampoco llegan a apagarse totalmente. Los transistores permanecen enteramente en sus regiones de operación en cualquier momento. Como resultado de esto los transistores no tienen un tiempo de almacenamiento de carga, y así pueden cambiar de estado mucho mas rápidamente. Por lo tanto la mayor ventaja de este tipo de lógica es su gran velocidad de transición.

El diagrama esquemático mostrado aquí esta tomado del manual de la series1000/10 000 de Motorola e dispositivos MECL. Este circuito en particular es de una compuerta OR/NOR de cuatro entradas. Los voltajes estándar para este circuito son -5.2 Volts (VEE) y tierra (VCC).Las entradas no utilizadas están conectadas a VEE. El circuito del lado derecho, consistente de un transistor y sus respectivas resistencias y diodos, pueden manejar cualquier número de compuertas en un solo encapsulado de Circuito integrado. Los circuitos integrados típicos incluyen compuertas dobles de 4 entradas, triples de 3 entradas y cuádruples de 2 entradas. En cada caso, las compuertas solo difieren en cuantos transistores de entrada poseen.

En operación, una salida lógica cambia de estado con solamente 0.85 Volts, desde -1.60 Volts para el cero hasta -0.75 para el uno. El circuito interno suministra un voltaje fijo de -1.175 Volts al transistor en el amplificador diferencia. Si todas las entradas están en -1.6 Volts ( o unidas a VEE) todos los transistores de entrada se apagarán y solamente el transistor diferenciador interno conducirá corriente. Esto reduce el voltaje de base del transistor de salida de la compuerta OR, bajando su voltaje de salida a -1.60 Volts. Al mismo tiempo ningún transistor de entrada esta afectando la base del transistor de salida de la compuerta NOR, así que su salida se dispara hasta -0.75 Volts. Esto es simplemente el voltaje base - emisor del propio transistor. Todos los transistores son parecidos dentro del circuito integrado y están designados para tener un voltaje de base - emisor de 0.75 Volts.

Cuando cualquiera de las entradas se eleva a -0.75 Volts ese transistor presenta corriente en el emisor causando que las salidas cambien de estado.

Los cambios de estado en este tipo de circuitos son pequeños, y están dictados por el voltaje base - emisor de los transistores involucrados cuando están encendidos. De mayor importancia para la operación del circuito es la cantidad de corriente fluyendo a través de varios transistores, esto es mas importante aun que los voltajes involucrados. Por lo tanto la lógica de emisor acoplado es también conocida como CML(current mode logic). Esto nos lleva a una desventaja de este tipo de compuertas: obtiene una gran corriente de la fuente de energía y sin embargo tiende a disipar una cantidad de calor significativa.

Para minimizar este problema, algunos dispositivos como los contadores de frecuencias usan contadores de décadas ECL en la entrada de circuito, seguida por TTL o contadores CMOS de alta velocidad en las posiciones digitales posteriores. Esto pone a los circuíos integrados rápidos y caros donde son absolutamente necesarios y nos permite utilizar circuitos integrados mas baratos en lugares donde las señales nunca serán de tan alta frecuencia.

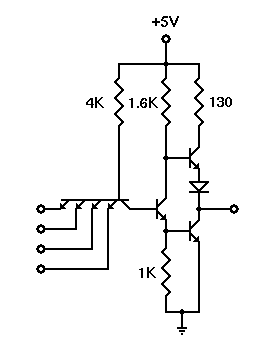

LÓGICA TRANSISTOR TRANSISTOR (TTL)

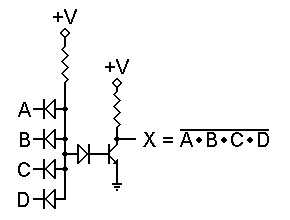

Con el desarrollo rápido de los circuitos integrados (ICs), fueron encontrados nuevos problemas fueron y las nuevas soluciones fueron desarrolladas. Uno de los problemas con los circuitos de DTL era que tomaba mucho mas espacio en la estructura del IC construir un diodo que un transistor. Puesto que las "propiedades inmobiliarias" son excesivamente importantes en ICs, era deseable encontrar una manera de evitar de requerir una gran cantidad de diodos en la entrada. ¿Pero qué se podía utilizar para sustituir muchos diodos? Bien, mirando la compuerta de DTL NAND en la parte de arriba, puede ser que observemos que los diodos opuestos se asemejan bastante a las dos ensambladuras de un transistor. De hecho, si tuviéramos un inversor, tendría un solo diodo de la entrada, y puede ser que se puedan sustituir los dos diodos opuestos por un transistor de NPN para hacer el mismo trabajo.

De hecho, esto trabaja absolutamente bien. La figura a la arriba demuestra el inversor que resulta. Además, podemos agregar emisores múltiples al transistor de la entrada sin preocuparnos del aumento de la cantidad de espacio necesaria en la viruta. Esto permite que construyamos una compuerta de múltiples entradas en el mismo espacio que un inversor. Los ahorros que resultan en propiedades inmobiliarias traducen al ahorros significativos en costes de la fabricación, que alternadamente reduce el coste al usuario del dispositivo.

Un problema compartido por todas las compuertas de la lógica con un solo transistor de la salida del colector es que el resistor es la velocidad de la conmutación. El transistor tira hacia abajo activamente la salida a la lógica 0, pero el resistor no está activo en tirar de la salida hasta la lógica 1. debido a los factores inevitables tales como capacitancias del circuito y una característica de transistores bipolares llamado "almacenaje de la carga," llevará cierta cantidad de tiempo al el transistor para dar vuelta totalmente a apagado y la salida se eleve a un nivel lógica 1. Esto limita la frecuencia en la cual la compuerta puede funcionar. Los diseñadores de las puertas comerciales del IC de la TTL redujeron ese problema modificando el circuito de salida. El resultado era "el circuito de salida del poste del totem" usado en la mayoría de la 7400/5400 serie TTL ICs. El circuito final usado en la mayoría en el estándar TTL se demuestra en la parte supeior. ¿El número de entradas puede variar? un paquete comercial del IC pudo tener seis inversores, cuatro compuertas 2-input, tres compuertas 3-input, o dos compuertas 4-input. Una compuerta 8-input en un paquete está también disponible. Pero en cada caso, la estructura del circuito sigue siendo la misma, difiriendo solamente el número de entradas.

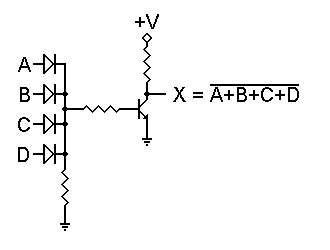

LÓGICA DIODO - TRANSISTOR

Como dijimos en la página de lógica del diodo, el problema básico con las puertas del DL es que deterioran rápidamente la señal lógica. Sin embargo, trabajan para una etapa a la vez, si la señal re-se amplifica entre las puertas. La lógica del Diodo-Transistor (DTL) logra esa meta.

La puerta a la parte superior es un DL o puerta seguida por un inversor tal como se vio en la página en lógica del resistor-transistor. La función OR todavía es realizado por los diodos. Sin embargo, sin importar el número de las entradas de la lógica 1, es seguramente bastante voltaje de entrada para conducir el transistor a la saturación. Solamente si todas las entradas están en 0 lógico entonces el transistor permanecerá apagado. La ventaja de este circuito sobre su equivalente de RTL es que la OR lógica es realizada por los diodos, al lado de los resistores. Por lo tanto no hay interacción entre diversas entradas, y cualquier número de diodos puede ser utilizado. Una desventaja de este circuito es el resistor de entrada al transistor. Su presencia tiende para retardar el circuito el estado bajo, limitando así la velocidad a la cual el transistor puede cambiar estados.

En el primer vistazo, la versión del NAND demostrada arriba debe eliminar este problema. ¿Cualquier 0 lógico de entrada tirará hacia abajo inmediatamente la base del transistor y cambiará al transistor al estado de apagado? Bien, no absolutamente. ¿Recuerda ese voltaje de entrada de la base de 0,65 voltios para el transistor? Los diodos exhiben un voltaje de polarización directa muy similar cuando están conduciendo la corriente. Por lo tanto, uniforme con todas las entradas en la tierra, la base del transistor estará en cerca de 0,65 voltios, y el transistor puede conducir.

Para solucionar este problema, podemos agregar un diodo en serie con la base del transistor, según lo demostrado arriba. Ahora el voltaje de polarización directa que se necesitó para polarizar al transistor directamente es 1,3 voltios. Para aún más seguro, podríamos agregar un segundo diodo de la serie y requerir 1,95 voltios para hacer conducir el transistor. De esta manera podemos también estar seguros que los cambios de temperatura no afectarán perceptiblemente la operación del circuito. Cualquier manera, este circuito trabajará como compuerta del NAND. Además, podemos utilizar tantos diodos en la entrada como podemos desear sin levantar el umbral del voltaje. Además, sin el resistor en serie en el circuito de entrada, hay menos efecto de retardado, así que la puerta puede cambiar estados más rápidamente y manejar frecuencias más altas.

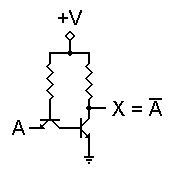

RESISTOR-TRANSISTOR LOGIC

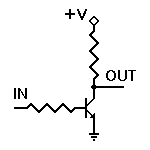

Considere el circuito más básico del transistor, tal como el que esta demostrado arriba. Aplicaremos solamente uno de dos voltajes a la entrada: 0 voltios (lógica 0) 0 5 voltios de +V (lógica 1). El voltaje exacto usado como +V depende de los parámetros de diseño de circuito; en RTL los circuitos integrados, el voltaje generalmente son +3.6v. que asumiremos un transistor ordinario de NPN aquí, con un aumento actual razonable de C.C. Un voltaje de polarización directa de la unión emisor-base de 0,65 voltios, y un voltaje de saturación del colector-emisor no más arriba de 0,3 voltios. En los IC RTL estándar, el resistor bajo es 470 ohmios y el resistor del colector es 640 ohmios.

Cuando el voltaje de entrada es cero voltios (realmente, cualquier cosa bajo 0,5 voltios), no existe polarización directa a la unión de emisor-base, y el transistor no conduce. Por lo tanto ninguna corriente atraviesa el resistor del colector, y el voltaje de la salida es 0 voltios de +V. Por lo tanto, una 0 lógico entró, resultando en una lógica 1 hecha salir. Cuando el voltaje de entrada es voltios de +V, la ensambladura de la emisor-base del transistor será polarizada directamente claramente. Nosotros asumimos un circuito de salida similar conectado con esta entrada. Así, tendremos un voltaje de 3,6 - 0,65 = 2,95 voltios aplicados a través de una combinación de la serie de la salida de 640 ohmios un resistor y un resistor de entrada de 470 ohmios. Esto nos da una corriente de la base de:

2.95v / 1110

= 0.0026576577 amperes = 2.66 mA.

RTL es relativamente una vieja tecnología, y los transistores usados en los IC's RTL tienen un aumento actual de la C.C. de polarización directa de alrededor 30. Si asumimos un aumento actual de 30, la corriente baja de 2,66 mA apoyará un máximo de la corriente de colector de 79,8 mA. Sin embargo, si caemos todos sino 0,3 voltios a través del resistor de 640 colectores, llevará 3,3/640 = 5,1 mA. Por lo tanto este transistor de hecho se satura completamente. Con un 1 lógico de entrada, este circuito produce una lógica 0 a la salida. Hemos visto ya que una 0 lógico en la entrada producirá un 1 lógico a la salida. Por lo tanto, esto es un circuito básico del inversor.

Como podemos ver de los cálculos antedichos, la cantidad de corriente proporcionada a la base del transistor es lejana y es mas que necesario para poner en conducción el transistor en la saturación. Por lo tanto, tenemos la posibilidad de usar uno para conducir las entradas múltiples de otras puertas, y así tener compuertas con los resistores de entrada múltiples. Tal circuito se demuestra en la figura de la parte superior. En este circuito, tenemos cuatro resistores de entrada. Levantar la entrada a +3,6 voltios será suficiente hacer conmutar al transistor, y la aplicación de entradas de la lógica adicional 1 (+3,6 voltios) realmente no tendrá ningún efecto apreciable en el voltaje de la salida. Recuerde que el voltaje del polarización directa en la base del transistor no excederá 0,65 voltios, así que la corriente a través de un resistor de entrada puesto a tierra no se excederá 0.65v/470 = 1,383 mA.

Esto nos provee a nosotros un límite práctico en el número de los resistores de entrada permisibles a un solo transistor, pero no causa ningunos problemas serios dentro de ese límite.

La puerta de RTL demostrada arriba funcionará, pero tendrá un problema debido a las interacciones posibles de la señal a través de los resistores de entrada múltiples. Una manera mejor de poner la función en ejecución se demuestra arriba. Aquí, cada transistor tiene solamente un resistor de entrada, Asegurando así que no exista ninguna interacción entre las entradas. La función se realiza en la conexión del colector común de todos los transistores, que comparten un solo resistor de la carga del colector. Éste es en hecho el patrón para todo IC RTL estándar. Se clasifica para dibujar , 12 mA de la corriente de la fuente de alimentación 3.6V cuando ambas salidas están en la lógica 0. Esto corresponde absolutamente bien con los cálculos que hemos hecho ya.

El fan-out estándar para las puertas de RTL es clasificado en 16. Sin embargo, el fan-in para una entrada de puerta estándar de RTL es 3. Así, una puerta puede producir 16 unidades de corriente de impulsión de la salida, pero requiere 3 unidades conducir una entrada. Hay versiones de baja potencia de estas compuertas que aumenten los valores de los resistores de la base y del colector 1.5K y 3.6K, respectivamente. Tales compuertas exigen menos, y tienen típicamente un fan-in de 1 y un fan-out de 2 o 3. También han reducido respuesta de frecuencia, así que no pueden funcionar tan rápidamente como las compuertas estándares.

Para conseguir mayores hacer salir capacidades de impulsión, los almacenadores intermediarios se utilizan. Éstos son típicamente los inversores que se han diseñado con un fan-out de 80. También tienen un requisito del fan-in de 6, puesto que utilizan pares de transistores de la entrada para conseguir la impulsión creciente.

Podemos conseguir una función NAND de cualquiera de las dos maneras. Podemos invertir simplemente las entradas a la puerta de NOR/OR, haciéndolo conmutar en una compuerta de AND/NAND, o se puede utilizar el circuito demostrado arriba. En este circuito, cada transistor tiene su propio resistor de entrada separado, así que cada uno es controlada por una diversa señal de entrada. Sin embargo, la única manera que la salida se puede fijar hacia abajo a la lógica 0 es si ambos transistores son conmutados por las entradas por un 1 lógico. El problema con este circuito del NAND proviene el hecho de que los transistores no son dispositivos ideales. ¿Recuerde ese voltaje de la saturación del colector de 0,3 voltios? Idealmente debe ser cero. Puesto que no es, necesitamos mirar qué sucede cuando "apilamos" los transistores. Con dos, el voltaje combinado de la saturación del colector es 0,6 voltios solamente levemente menos que el voltaje de la base de 0,65 voltios que hará conmutar al transistor.

LÓGICA DE DIODO

La lógica del diodo hace uso del hecho de que el dispositivo electrónico conocido como diodo conducirá una corriente eléctrica en una dirección, pero no en la otra. De este modo, el diodo actúa como interruptor electrónico.

A la izquierda usted ve una lógica básica OR del diodo. Asumiremos que una lógica 1 es representada por +5 voltios, y una lógica 0 es representada por la tierra, o cero voltios. En esta figura, si ambas entradas se dejan no relacionadas o son ambas en la lógica 0, la salida Z también será llevada a cabo en cero voltios por el resistor, y será así un 0 lógico también. Sin embargo, si cualquier entrada se levanta a +5 voltios, su diodo se polarizará directamente y por lo tanto conducirá. Esto alternadamente forzará para hacer salir hasta el 1 lógico. Si ambas entradas son un 1, la salida todavía será 1. Por lo tanto, esta compuerta realiza correctamente una función lógica OR. A la derecha está el equivalente a la compuerta AND. Utilizamos los mismos niveles de la lógica, pero se invierten los diodos y el resistor se fija para tirar del voltaje de la salida hasta un 1 lógico. Para este ejemplo, se utilizan +V = +5 voltios, aunque otros voltajes pueden hacerlo fácilmente. Ahora, si ambas entradas son no relacionadas o si son ambas en 1, la salida Z estará en 1 también. Si se pone a tierra cualquier entrada (0 lógico), ese diodo conducirá y tirará hacia abajo la salida a un 0 lógico también. Ambas entradas deben ser 1 en la orden para que la salida sea la lógica 1, así que este circuito realiza la función lógica AND.

En ambas compuertas, hemos asumido que los diodos no introducen ningunos errores o pérdidas en el circuito. Éste no es realmente el caso; un diodo de silicio experimentará una caída de voltaje de polarización directa de alrededor 0.65v a 0.7v mientras que conduce. Pero podemos remediar esto especificando que cualquier voltaje sobre +3,5 voltios sea la lógica 1, y cualquier voltaje debajo de +1,5 voltios será la lógica 0. Es ilegal en este sistema que un voltaje de la salida esté entre +1,5 y +3,5 voltios; ésta es la región indefinida de voltaje en la cual el sistema no sabe de que manera responder.

Las puertas individuales como las dos de arriba se pueden utilizar circunstancias específicas. Sin embargo, cuando se conectan en cascada las puertas del DL, según lo demostrado arriba, algunos problemas adicionales ocurren. Aquí tenemos dos compuertas AND, cuyas salidas están conectadas con las entradas de una compuerta AND. Si fijamos hacia abajo las entradas a un 0 lógico, seguramente la salida será llevada a 0. ¿Sin embargo, si en ambas entradas de cualquier compuerta AND están en +5 voltios, cuáles será el voltaje de salida? El diodo en la compuerta OR será polarizado directamente inmediatamente, y la corriente atravesará el resistor de la puerta AND, a través del diodo, y a través del resistor de la compuerta OR. Si asumimos que todos los resistores son de valores igual (típicamente), actuarán como divisor del voltaje y compartirán igualmente el voltaje de fuente de +5 voltios. El diodo de la compuerta OR insertará su pequeña pérdida en el sistema, y el voltaje de la salida será cerca de 2,1 a 2,2 voltios. Si ambas compuertas AND tienen entradas en 1, el voltaje de la salida puede levantarse hasta cerca de 2,8 a 2,9 voltios. Claramente, esto está en la "zona prohibida," que no se supone no está permitida.

Si vamos un paso más lejos y conectamos las salidas de dos o más de estas estructuras con otra compuerta AND, habremos perdido todo el control sobre el voltaje de la salida; habrá siempre un diodo polarizado inversamente en alguna parte que bloquea las señales de entrada y que evita que el circuito funcione correctamente. Esta es la razón por la cual la lógica del diodo se utiliza solamente para las compuertas solas, y solamente en circunstancias específicas.

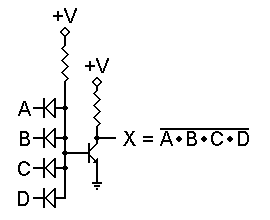

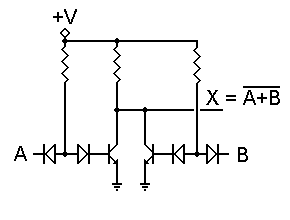

LOGICA CMOS

La lógica del CMOS es una más nueva tecnología, basada en el uso de los transistores complementarios del MOS de realizar funciones de la lógica con casi ningún componente. Esto hace estas puertas muy útiles en usos con pilas. El hecho de que trabajarán con los voltajes de fuente de hasta sólo 3 voltios y tan arriba como 15 voltios son también muy provechosos

Todas las compuertas del CMOS se basan en el circuito fundamental del inversor demostrado arriba. Observe que ambos transistores son MOSFET's del enriquecimiento; un canal N con su fuente puesto a tierra, y un canal P con su fuente conectada a +V. Sus compuertas están conectados juntos para formar la entrada, y sus drenajes están conectados juntos para formar la salida. Los dos MOSFET's se diseñan para tener características semejantes.

Así, son complementarios el uno al otro. Cuando está apagado, su resistencia es con infinita; cuando está encendido, su resistencia del canal es cerca de 200 ohmios. Puesto que la puerta es esencialmente un circuito abierto por el cual no circula ninguna corriente, y el voltaje de la salida será igual al voltaje de la fuente de alimentación, dependiendo de el cual el transistor está conduciendo.

Cuando se pone a tierra la entrada A (0 lógico), el MOSFET del canal N es imparcial, y por lo tanto no tiene ningún canal de enriquecimiento dentro de sí mismo. Es un circuito abierto, y por lo tanto sale de la línea de salida desconectada de la tierra.

En el mismo tiempo, se polariza directamente el MOSFET del canal P, así que tiene un canal de enriquecimiento dentro de sí mismo. Este canal tiene una resistencia de cerca de 200 ohmios, conectando la línea de salida con la fuente de +V. Esto fija la salida hasta +V (1 lógica). Cuando la entrada A está en +V (1 lógico), el MOSFET del canal P está apagado y el MOSFET del canal N encendido, así está fijando la salida a la tierra (0 lógico).

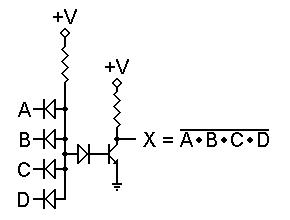

Este concepto se puede ampliar en las estructuras AND y NAND combinando los inversores parcialmente en una serie, en estructura parcialmente paralela. El circuito de arriba es un ejemplo práctico de un CMOS 2 entradas. En este circuito, si ambas entradas son bajas, ambos MOSFET's del canal P serán conmutados, así al abastecimiento de una conexión a +V. Ambos MOSFET's del canal N estarán apagados, Asegurando así que no exista ninguna conexión de tierra. Sin embargo, si pasa a ALTO cualquier entrada, ese MOSFET del canal P conmutará a apagado y desconectará a la salida de +V, mientras que ese MOSFET del canal N conmutará, así poniendo a tierra la salida.

La estructura se puede invertir, según lo demostrado en la parte superior. Aquí tenemos una compuerta NAND de dos entradas, donde una 0 lógico en cualquier entrada forzará la salida a un 1 lógico, pero toma ambas entradas en 1 para permitir que la salida vaya a 0. Esta estructura es menos limitada de lo que sería el equivalente bipolar, pero todavía hay algunos límites prácticos. Uno de éstos es la resistencia combinada de los MOSFET's en serie. Consecuentemente, los postes del CMOS no se hacen de más de cuatro entradas altas. Las compuertas con más de cuatro entradas se construyen como las estructuras de conexión en cascada preferentemente que estructuras solas. Sin embargo, la lógica sigue siendo válida. Incluso con este límite, la estructura del poste todavía causa algunos problemas en ciertos usos.

LÓGICA CTL (COMPLEMENTARY TRANSISTOR LOGIC)

Significa Lógica de complementación de transistor y sus características son las siguientes.

| Retraso de propagación por compuerta | Consumo promedio por compuerta |

| 5 nano-segundos | 50 nano-Watts |

LÓGICA I 2 L ( INTEGRATED INJECTION LOGIC)

Significa lógica de inyección integrada y la principal ventaja de este tipo de integrados es que permite una alta densidad de integración, similar a la de los dispositivos MOS, y también un bajo consumo de potencia.

| Retraso de propagación por compuerta | Consumo promedio por compuerta |

| 40 nano-segundos | Menor que 1 mili-Watt |

LÓGICA MOS (METAL OXIDE SEMICONDUCTOR)

Significa lógica de oxido de semiconductor metálico, se caracteriza porque emplean transistores de efecto de campo que tienen las ventajas de mayor facilidad de fabricación, tamaño mas pequeño (1/50 de transistores bipolares)y muy baja disipación de potencia. Las desventajas son baja velocidad de respuesta, mayor delicadeza en el manejo y poca capacidad de manejo de corriente.

LÓGICA PMOS (P CHANNEL METAL OXIDE SEMICONDUCTOR)

La característica de esta familia es que requieren solo la tercera parte de pasos necesarios de producción de su contraparte con transistores bipolares estándar de doble difusión.

LÓGICA NMOS (N CHANNEL MOS)

Permiten el doble de densidad de integración que los P-MOS, además de ser casi dos veces mas rápidos debido a que en NMOS los portadores de carga son los electrones libres (mientras que en PMOS los portadores de carga son los huecos que son mas lentos).

| Retraso de propagación por compuerta | Consumo promedio por compuerta |

| 40 nano-segundos | Menor que 1 mili-Watt |

LÓGICA HMOS (HIG DENSITY MOS)

Tienen la característica de que permiten una alta capacidad de integración.

LÓGICA SOSMOS (SILICON ON SAPHIRE MOS)

Está lógica se caracteriza por emplear un sustrato de aislante en lugar del sustrato semiconductor tradicional con lo que logran frecuencias mayores de 50 Mega Hertz con un consumo de potencia del orden de un nano-Watt. Las características del material aislante que utilizan estos circuitos integrados agrava su precio de manera considerable, siendo utilizado solamente en circuitos de conmutación de alta velocidad.

LÓGICA RTL

| Retraso de propagación por compuerta | Voltaje de alimentación | Margen de Ruido | Consumo promedio por compuerta |

| 50 nano-segundos | 3 Volts | 0.2 Volts | 10 mili-Watts |

LÓGICA DTL

| Retraso de propagación por compuerta | Voltaje de alimentación | Margen de Ruido | Consumo promedio por compuerta |

| 25 nano-segundos | 5 Volts | Bajo | 15 mili-Watts |

LÓGICA TTL (En general)

| Voltaje de alimentación | Margen de Ruido |

| 5 Volts | 0.4 Volts |

TTL ESTANDAR (SERIE 54 / 74)

Retraso de propagación por compuerta de 10 nano segundos.

Disipación por compuerta de 10 miliwatts.

TTL ALTA VELOCIDAD (SERIE 54 / 74H)

Retraso de propagación por compuerta de 6 nano segundos.

Disipación por compuerta de 22 miliwatts.

TTL BAJO CONSUMO (SERIE 54 / 74L)

Retraso de propagación por compuerta de 33 nano segundos.

Disipación por compuerta de 1 miliwatt.

TTL SCHOTTKY (SERIE 54 / 74S)

Retraso de propagación por compuerta de 3 nano segundos.

Disipación por compuerta de 19 miliwatts.

TTL SCHOTTKY DE ABJO CONSUMO (SERIE 54 / 74LS)

Retraso de propagación por compuerta de 9.5 nano segundos.

Disipación por compuerta de 2 miliwatts.

EMITTER COUPLED LOGIC

Puede operar a frecuencias mayores de 500 Mhz.

Retraso de propagación por compuerta de 0.3 nano segundos.

Disipación por compuerta de 60 miliwatts.

Descargar

| Enviado por: | Memphis |

| Idioma: | castellano |

| País: | México |