Informática

Evolución de los Microprocesadores (INTEL-AMD). K7 (Athlon)

4.6.- K7 (Athlon) de AMD

Parece que AMD sigue siempre el camino marcado por Intel, y en esta ocasión también se ha apuntado a cambiar los juegos de números por las palabras más o menos altisonantes.

Si Intel denominó Pentium al i586, AMD ha hecho lo propio con el K7.

Pero no nos engañemos, marketing a un lado, la verdad es que este nuevo procesador tiene unas características técnicas que deberían posicionarle incluso por encima de los Pentium III de Intel, pero como siempre, este factor por sí solo no proporcionará a esta nueva plataforma la aceptación que AMD tanto necesita.

A pesar del éxito obtenido por AMD con su gama K6, Intel contraatacó muy fuerte con sus nuevos Celeron de 128 Kb y su zócalo 370, y AMD necesita que el Athlon sea todo un éxito para dejar atrás los números rojos en los que está sumergida.

Pero para ello necesita contar con el soporte de la industria informática y acertar en el marketing, así como evitar los problemas de producción que tuvo con los K6. Por último y no menos importante, rezar para que Intel tarde lo máximo posible en reaccionar.

Empezaremos por decir que los nuevos modelos utilizan un nuevo zócalo totalmente incompatible con todo lo conocido hasta ahora en el mundo PC, aunque está basado en el EV6 de los Alpha de Digital, y su conector, conocido como Slot A, es idéntico físicamente al Slot1 de Intel.

Este bus trabaja a velocidades de 200 Mhz, en contra de los 100 de los modelos actuales, y están previstos modelos futuros a 400 Mhz. La memoria de primer nivel cuenta con 128 KB (cuatro veces la de los Pentium III) y la L2 es programable, lo que permite adaptar la cantidad de caché a distintas necesidades, contando en un principio con 512 KB, pero estando previstos modelos con hasta 8 MB.

Los modelos iniciales trabajan a 500, 550 y 600 Mhz y siguen estando fabricados con la tecnología actual de 0,25 micras. Incorporan 22 millones de transistores. Por supuesto soporta las instrucciones 3DNow.

Por fin la arquitectura soporta sistemas multiprocesador con los juegos de chipset adecuados, pudiéndose construir máquinas con hasta 8 micros o más.

4.6.1.- AMD K7 al detalle.

Después que Intel anuncia su siguiente procesador, “el que acabaría con la competencia”, aparece AMD con su K7, con una propuesta fuerte y arriesgada, porque abandona su hasta ahora plaza fuerte que es el Socket 7, donde se conectaban los Pentiums clásicos y se pasa, por primera vez, a un conector propietario, el Slot A. Veamos sus características.

El bus : El Slot A, y por tanto el AMD K7, no utilizaran el protocolo de bus de Intel P6 GTL+, sino que implementaran el EV6, utilizado por los Alpha de Digital EV6 que tiene muchas ventajas sobre el GTL+, como la "topología punto a punto" para multiproceso simétrico. Como novedad incluso sobre el EV6 implementado para los Alpha, el bus del K7 alcanzara los 200 MHz, dejando muy atrás las previsiones de Intel para sus próximos productos (anunciado hasta 133 MHz) o los actuales (100 MHz con chipsets BX). Con esta velocidad de bus es cuando realmente empieza a tener sentido las nuevas memorias directas, como la RDRAM o la DDR-SDRAM. Por ejemplo, la RDRAM corriendo a 100 MHz ofrece una máxima de 1.6 GB/s, mientras que el bus GPL+ de Intel solo absorbe, funcionando a 100 MHz, 800 MB/s, y funcionando a 133 MHz alcanza los 1066MB/s. El máximo alcanzado por la RDRAM solo lo puede manejar en su totalidad el bus EV6 a 200 MHz del K7.

La cache primaria: El K7 tendrá, como mínimo, 128 KB de cache de primer nivel (L1 cache), repartidas entre 64 KB para datos y 64 KB para instrucciones. Contara, por tanto, con cuatro veces mas cache de primer nivel que los actuales Pentium II que disponen de 32 KB (16+16). Parece ser que los Katmai dispondrán de 64 KB (32+32). Una cache de primer nivel de gran tamaño solo tiene sentido para procesadores que funcionen a una frecuencia interna muy elevada, para evitar los estados de espera del microprocesador y poder aprovechar completamente el paralelismo (pipelining) implementado. Y el K7 funcionara muy rápido.

La cache secundaria: El K7 será bastante flexible en este punto. Vendrá con una cache "backside", como la implementada en la arquitectura P6 de Intel. El K7 dispone de una tag RAM interna suficiente para manejar 512 KB de cache L2, pero AMD planea también versiones del K7 con no menos de 2 MB, pudiendo llegar a los 8 MB de cache de segundo nivel, utilizando una tag RAM adicional externa, como hace Intel en el caso de los P6 (PPro). La velocidad de esta cache variara entre 1/3 de la frecuencia del micro hasta la misma frecuencia (recordemos, del microprocesador no del bus). Podrá utilizar tanto RAM "normal" como SRAMs de "doble flujo de datos" (DDR : Double Data Rate). Toda esta flexibilidad en la cache secundaria permitirá a AMD ofrecer varias líneas de su K7, para rangos de publico variando desde el nivel domestico hasta servidores de altas prestaciones.

Velocidades de reloj: El AMD K7 ya funcionan en estos momentos a 500 MHz, pero al momento de su lanzamiento, se habrá superado esta cifra ampliamente. El K7 dispone de buffers realmente profundos para poder conseguir estas velocidades tan elevadas, pudiendo llegar a tener 72 instrucciones x86 ejecutándose.

La unidad de Punto Flotante (FPU): El proceso en punto flotante ha sido siempre la asignatura pendiente de AMD. Pues bien, todos nos preguntábamos hasta cuando. Pues hasta el K7 ni mas ni menos. El AMD K7 dispondrá de 3 Líneas de ejecución (pipelines), totalmente paralelas y con ejecución fuera de orden (out-of-order execution). Literalmente, el K7 pulverizara el rendimiento de cualquier micro actual de Intel y de los próximos que ha anunciado.

La arquitectura del microcódigo: La entrada al microprocesador cuenta con tres decodificadores de instrucciones x86, que trasladan las instrucciones x86 a "MacroOps", operaciones de longitud fija para que sean tratadas por el microprocesador. Las operaciones de longitud fija son una de las bases de la filosofía RISC. Estos tres decodificadores alimentan con "MacroOps" a la unidad de control de instrucciones de 72 entradas. Cada una de estas "MacroOps" consisten en una o dos operaciones. Hay dos maneras de decodificar las instrucciones x86, el "DirectPath" (camino directo) que como su nombre indica efectúa una conversión directa y por tanto, muy rápida, y el "VectorPath" (camino por vectores) que utiliza una tabla de traducciones en ROM, llamada MROM(MacroCodeROM). Una vez las instrucciones son decodificadas pasan a la unidad de control de instrucciones, donde pueden esperar hasta 72 de ellas. Esta unidad las va enviando, según corresponda, al Planificador de Enteros (Integer Scheduler) o a la unidad FPU/Multimedia. El planificador de enteros puede almacenar hasta 15 MacroOps, representando hasta 30 operaciones (recordemos que cada MacroOp puede contener una o dos operaciones). Su trabajo es distribuirlas entre las tres unidades de ejecución paralelas, cada una de las cuales esta acompañada de una unidad de generación de direcciones, responsable de los accesos a memoria. Estas unidades se encargan de optimizar el acceso a la cache de primer y segundo nivel, para minimizar el tiempo de respuesta.

Se podría concluir que Intel lo tiene difícil esta vez. Hay que tener en cuenta varios factores. Hoy por hoy, la base de K6-2 es enorme y crece rápidamente, por lo que el soporte para 3DNow! esta aumentando. DirectX 6

esta optimizado para utilizarlo, y MMX ha resultado no servir para nada. Intel saco su Katmai, que implemento con el KNI (MMX2) muy similar, aunque superior, al 3DNow!, pero al ser el ultimo procesador de Intel, como siempre, su precio es elevado y por tanto 3DNow! continuara avanzando.

El único defecto que se le puede achacar al K7 es la utilización de un bus propietario, el Slot A, y por tanto de un chipset propio. Pero hoy por hoy para ir al día hay que comprar una nueva tarjeta madre con cada nuevo procesador, por lo que de hecho no es ningún defecto. Dicho todo esto, no hay que olvidar a alguien que ha estado últimamente muy en las sombras... CYRIX. Habrá que esperar que dicen ellos en esta disputa de INTEL y AMD.

4.6.2.- Presentación Tecnológica del AMD K7

Descripción del procesador AMD-K7(TM)

-

Diseño de la CPU de Séptima generación.

-

Funcionamiento principal en enteros, punto flotante, y multimedia.

-

Frecuencias de funcionamiento de 500 MHz+ usando tecnología de 0.25mm.

-

Tecnología Del bus Ev6 De Alpha(TM) de alta Velocidad.

-

Controlador de Cache de nivel 2 de Alto Velocidad.

-

Arquitectura del multiprocesamiento escalable para los mercados del workstations y servidores.

-

Módulo del procesador para los factores estándares de la forma de la tarjeta madre.

-

Chipsets optimizado, tarjetas madres y BIOS.

Arquitectura del procesador AMD-K7(TM)

-

Tres decodificadores paralelos de la instrucción x86.

-

9-issue de microarquitectura superescalar optimizada para alta frecuencia.

-

Programación dinámica con ejecución especulativa, ejecución out-of-order.

-

Tabla de predicción de ramificación de 2048 entradas y pila de retorno de 12 entradas.

-

3 Superescalares , con pipelines enteras y out-of-order, cada uno contiene:

-

Unidad de ejecución de enteros.

-

Unidad de generación de direcciones.

-

3 Superescalares, pipelines de multimedia out-of-order con rendimiento de procesamiento de 1 ciclo:

-

FADD (4 ciclos de latencia), MMX ALU (2 ciclos de latencia), 3DNow!.

-

FMUL (4 ciclos de latencia), MMX ALU (incluye Mul y MAC), 3DNow!.

-

FSTORE.

-

I-Cache de Nivel 1 de 64K y D-Cache de 64K, cada uno con un conjunto bidireccional asociado.

-

TLB de varios niveles (24/256-Entradas I, 32/256-Entradas D).

-

Dos puertos de carga/almacenamiento(Load/Store) de 64-bit de propósito general dentro de la D-Cache :

-

3 Ciclos de latencia para la carga.

-

Las Múltiples actividades bancarias permiten el acceso concurrente por 2 Load/Stores.

-

Controlador de cache L2 de 64 Bits de alta velocidad:

-

Apoya tamaños de 512KB a 8MB.

-

Velocidades programables de la interfaz.

-

Interfaz de sistema de 64 Bits de la alta velocidad:

-

Primeros sistemas de corriente para tener un bus de 200MHz.

-

Un espacio libre significativo para el futuro.

-

Buffer interno profundo para utilizar pipelines e interfaces externos:

-

Hasta 72instrucciones x86 durante el vuelo.

-

Falta excepcional de la carga 32.

-

Planificador de trabajos de números enteros de 15 entradas.

-

Planificador de trabajos de Punto flotante de 36 entradas.

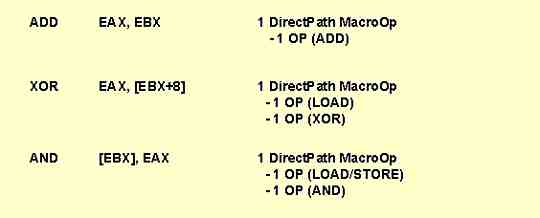

Terminología de la Microarquitectura.

-

Las instrucciones x86 se envían a una de las dos pipelines de decodificación.

-

DirectPath: Decodifica las instrucciones comunes x86 (1-15 bytes de largo).

-

VectorPath: Decodifica las instrucciones poco comunes y complejas x86.

-

Las pipelines de decodificación pueden enviar 3 MacroOps a los planificadores de trabajos de la unidad de la ejecución.

-

Cada MacroOp consiste en una o dos operaciones (OPs).

-

OPs son publicadas (issues) a las unidades de la ejecución.

Fig. Nro. 4.6.a, Terminología de la Microarquitectura

Microarquitectura del Pipeline

Fig. Nro. 4.6.b, microarquitectura del Pipeline

Diagrama de Bloques del Procesador AMD-K7(TM)

Fig. Nro. 4.6.c, Diagrama de bloques del procesador K7

Decodificador de Instrucciones x86

Fig. Nro. 4.6.d, decodificador de instrucciones x86

Unidades De Ejecución Enteras

-

Tres Unidades De Ejecución De enteros (Ieu).

-

Tres Unidades De Generación de Direccionamientos (Agu).

-

Planificador de trabajos de enteros de 15 entradas.

-

Ejecución Especulativa out-of-order Completa.

-

Multiplicador.

Fig. Nro. 4.6.e, Unidad de ejecución de enteros

Unidades De Ejecución Multimedia De Superscalares.

-

Tres Unidades De Ejecución De Multimedia De los Superscalares.

-

3-issue, out-of-order, diseño completamente canalizado(pipelined).

-

Archivo de Registros separados.

Fig. Nro. 4.6.f, Unidades De Ejecución Multimedia De Superscalares.

Cache de Unidad de carga/almacenamiento y de los datos.

-

Unidad Del Almacén De la Carga (Lsu).

-

Cola de carga/almacenamiento de 44 entradas.

-

Expedición de los datos de almacenes a las cargas dependientes.

-

Cache bidireccional de datos de dos puertos de 64KB.

-

Coherencia de MOESI, tamaño de la línea de 64 bytes.

-

DTLB L1 de 32 entradas y 4 vias, conjuntos DTLB L2 de 256 entradas.

-

3 conjuntos de datos de cache .

Fig. Nro. 4.6.g, Cache de Unidad de carga/almacenamiento y de los datos.

Sistema controlador de Interfaz Interno.

Fig. Nro. 4.6.h, Sistema controlador de Interfaz Interno.

Interfaces del sistema y de la cache L2.

-

Protocolo Del bus De Alfa Ev6.

-

Topología del Punto a punto con la expedición del reloj.

-

Bus de datos y de l direccionamiento

-

bus de datos de 72 bits con ECC

-

bus independiente de Address/Request

-

bus independiente de Snoop.

-

Hasta 20 transacciones excepcionales por procesador.

-

Multiprocesamiento escalable.

-

Interfaz De la cache L2:

-

SRAMs estándares de 512KB a 8MB usandas en la industria

-

velocidades programables de la interfaz.

-

Señalizacion de bajo voltaje.

Fig. Nro. 4.6.i, Interfaces del sistema y de la cache L2.

Infraestructura Del Procesador Amd-k7(tm).

-

Chipsets

-

los chipsets de Funcionamiento optimizado AMD-k7 son planeados tanto por AMD como por los vendedores a terceras personas que lideran en 1999.

-

Tarjetas Madre:

-

La alta calidad, las tarjetas madres de funcionamiento optimizado de AMD-k7 son planeadas por los vendedores principales de 1999.

-

BIOS:

-

El BIOS de la producción se planea entre todos los proveedores principales incluyendo AMI, Award y Phoenix.

-

Mecánico:

-

El procesador AMD-k7 utilizará componentes estandares de la industria existentes en los componentes de la infraestructura fisica y mecanica incluyendo casos, fuentes de alimentación, ventiladores, los disipadores de calor, el etc.

5.- COMPARACIONES

5.1.- Comparativa entre K6-3 y PIII.

Ya están saliendo los testeos y comparativas con auténticos Pentium III y K6-III de serie, no con prototipos. De entrada sustituyo en la denominación de ambos microprocesadores la numeración romana "III" por la más cómoda "3". Mis impresiones personales sobre los nuevos micros, tanto el de Intel como el de AMD, es que aportan 'ligeras' mejoras sobre los microprocesadores ya existentes.

Puntualizando muy brevemente para cada microprocesador en concreto:

El P3 sólo parece que sacará ventaja respecto a sus hermanos P2 a la misma frecuencia, con programas optimizados para las MMX-2. En consecuencia, para equipos de sobremesa de propósito general los microprocesadores de Intel más aconsejables, de momento, siguen siendo los P2. La relación precio/prestaciones: excelente en los P2 y Mala (por el tema precio) para P3. Como casi siempre ocurre con Intel, lo mejor del P3 vendrá cuando aparezcan sus derivados, tanto para el mercado de precios bajos, como las generaciones en tecnología de 0.18 micras con multiplicadores adecuados para funcionar sin ningún problema en FSB a 133 Mhz y alcanzando frecuencias superiores a los 700 Mhz. Muy a tener en cuenta será el modelo cuya denominación en clave es "Coppermine" que tendrá una cache L2 de 256K integrada en el microprocesador (no en la PCB) y funcionando a la misma frecuencia que el microprocesador (no a la mitad).

El K6-3 parece ser la última maravilla del K6. No incorporará la tan bullada reforma (ya anunciada para su K7) de su FPU, es decir, no hay más reforma a la FPU del K6 que la introducida con el tema de las 3DNow en los K6-2. Según los tests, el incremento de prestaciones del K6-3 está basado en el rendimiento de las 256K de L2 a la misma velocidad del micro. Para aplicaciones de uso no intensivo de FPU, es decir, basadas en enteros, los K6-3 superan a los P2/P3 de su misma frecuencia. Pero en las aplicaciones que hacen uso intensivo de FPU son ostensiblemente inferiores a los microprocesadores de Intel. En consecuencia, los K6-3 seguirán siendo una interesante alternativa para equipos destinados a oficina si sus precios son parejos al de los Pentium de frecuencia similar.

5.2.- AMD K7 v/s INTEL Pentium III

Mirados desde el exterior son casi idénticos, el K7 y el Pentium III, pero internamente trabajan muy diferentemente. K7 es mucho más joven y significativamente más fuerte especialmente debido a sus enormes caches. Pero el Pentium III puede también es capaz de alcanzar algunos (pocos) puntos más arquitectónicos.

Cuando el desarrollador principal de AMD, Dirk Meyer, introdujo los fundamentos de la configuración arquitectónica de Athlon, en el foro del microprocesador en San Jose en octubre de 1998 (posteriormente el procesador fue llamado K7), impresiono a más de 1500 asistentes, entre ellos numerosos empleados de Intel, los cuales quedaron obviamente impresionados.

El Chip de AMD con 22 millones de transistores puede mostrar de hecho datos impresionantes. Hasta nueve unidades de función están trabajando en paralelo al mismo tiempo: tres unidades iguales de enteros (IEU), tres para el cálculo de direcciones y tres de unidades de punto flotantes/MMX/multimedia. Adicionalmente hay otras unidades como la unidad de carga/almacenamiento y unidad ramifica(Branch).

Lo que todos saben: Los primeros prototipos de K6-3d fueron equipados ya con pipelines de enteros. Sin embargo, el decodificador no podía proveer datos lo suficientemente rápido. Por lo tanto la tercera pipeline casi nunca era ocupada y seguía estando ociosa. Así AMD la quitó del diseño final. Las cosas son diferentes ahora con el K7: el decodificador de instrucciones es capaz de decodificar tres instrucciones x86 por el reloj y de distribuirlas a las unidades. Como el K6 cambia la instrucción x86 1:1 en instrucciones básicas simplemente estructuradas, llamadas ROPs que son construidas bajo el esquema de RISC. Adicionalmente hay un cuarto decodificador que interpreta las instrucciones complejas con un ' camino del vector '('vector path') y microcodigo de ROM y las altera además en varios ROPs.

K7 es capaz de almacenar hasta 72 de estos ROPs decodificados temporalmente en su ' unidad de control de instrucción '. El Pentium III tiene solamente dos decodificadores trabajando directamente en paralelo que son apoyados por un decodificador lento especial con la interpretación del microcódigo para las instrucciones complejas.

K7 es capaz de decodificar tres instrucciones simples x86 en paralelo (camino directo, Direct Path ); un cuarto decodificador es responsable de las instrucciones complejas (camino del vector).

La figura Nro. 5.2.a muestra en detalle esta decodificación.

Fig. Nro. 5.2.a, decodificación de instrucciones.

Los decodificadores modifican las instrucciones x86 en las operaciones que son llamadas como el RISC; el almacenamiento temporal de OPS. llamado 'estación de la reservación ' toma hasta 20 OPS que se puede distribuir a once unidades que computan pero solamente vía cinco accesos. Cada acceso es capaz de transmitir un OP por ciclo de reloj. Lo que significa un máximo de cinco instrucciones simultáneamente. Hay dos unidades de ejecución de enteros (acceso 0 y 1). El acceso 0 recoge además una variedad de unidades: una unidad de división entera (tiempo de ejecución por DIV: 20 ciclos de reloj), una unidad de rotación (Shift) y tres unidades FPU para FMUL, FDIV y FADD. El acceso 1 también se utiliza para ramificar ejecución. Los otros accesos son reservados para el almacenamiento de datos y los cálculos del direccionamiento.

5.2.1.- Mostrando su Pipeline (tubería)

En los foros como foro del microprocesador, los desarrolladores divulgan las tuberías que han desarrollado. Aparte de diagramas de bloque éstas son la tarjeta de visita del procesador.

Las tuberías deben tener una longitud adecuada. Si son demasiado cortas (underpipelined) la cantidad de paralelismo es demasiado baja. Adicionalmente cada etapa debe trabajar relativamente duro para mantener el reloj posible de la tubería bajo. Sin embargo, si son demasiado largos (overpipelined) permiten una alta frecuencia de reloj pero reaccionan muy alérgico a las ramificaciones del programa porque toma un cierto tiempo antes de que la tubería se llene otra vez. Los cómputos teóricos mostraron que cerca de ocho a nueve etapas son óptimas para las pruebas patrones clásicas del número entero. Con diez relojes K7 esta muy cerca del grado óptimo teórico mientras que el Pentium III con 12 a 17 relojes (parcialmente aún más) parece absolutamente overpipelined.

Con diez etapas, la tubería del K7 está en el área del grado óptimo teórico, la Figura Nro. 5.2.b muestra esta realidad.

Fig. Nro. 5.2.b, Tubería del K7

Desde la perspectiva del diseño la situación parece incluso peor para el Chip bastante antiguo de Intel con respecto al punto flotante. Aunque Intel nunca ha publicado la tubería los tiempos de espera sugieren cerca de 30 etapas comparadas a las 15 etapas del K7.

Para los procesadores con tuberías más largas la predicción de la ramificación debe ser lo mas exacta posible. K7 maneja dos vectores grandes para que este propósito recuerde el comportamiento de la ramificación de los Direccionamientos de la ramificación del último (BHT: Vector de la historia de la ramificación) y los objetivos (target) de la ramificación (BTB: Almacenador intermediario de los objetivos de la Ramificación). El BHT consiste en 4096 contadores individuales de 2-bits; en el BTB pueden caber 2048 Direccionamientos. Supuestamente las unidades de ramificación alcanzan un porcentaje medio de 95 por ciento. El Pentium III tiene una unidad levemente más simple para la predicción que trabaja con un Almacenador intermediario de objetivos de la ramificación de 512 entradas. En este caso el porcentaje medio debe solamente ser justo sobre el 90 por ciento.

Ambos utilizan un truco para las subrutinas que Cyrix ya había introducido con el 5x86: la pila de vuelta( the return stack). Usualmente las rutinas llamadas con CALL son también se terminadas con RET. El procesador memorizaba la dirección del return tan bien como estados de la tubería y del prefetch en una pila interna y no necesita esperar hasta que el return de la pila sea leído de la cache o de la memoria principal y los bytes hayan sido leídos y hayan sido decodificados en el objetivo de la ramificación. Esto puede ahorrar grandes cantidades de tiempo para el circuito y para las subrutinas llamadas a menudo. K7 se jacta aquí con una pila de vuelta de 12 etapas (K6 incluso tiene 16), lo cual puede ser exagerado levemente. Similar a su abuelo el Pentium Pro el Pentium III utiliza probablemente solamente cuatro etapas, lo cual es quizás demasiado pequeño.

5.2.2.- Cache Croesus

De acuerdo a esto la arquitectura de datos del K7 es generalmente un dígito binario ' más poderoso ' que el que Intel tiene. Adicionalmente las Caches L1 son cuatro veces más grandes (dos de 64 Kbytes en vez de dos de 16 Kbytes), así que uno habría podido contar con el K7 que tenía incluso ventajas más grandes de funcionamiento sobre el Pentium III. La Cache de instrucciones es actualmente de 92 Kbytes porque también almacena dígitos binarios 'precodificados'.

Similar al Pentium III la cache L2 reside externamente en el módulo y también se ejecuta a la mitad de la velocidad del procesador. Pero K7 es más flexible y permite diversas velocidades L2 a partir de la 1:1, de 2:3, de 1:2 y de 1:3. Mientras que en el Pentium III el controlador del cache esta como componente separado en el módulo, la versión de K7 se integra en el modulo. Esta soporta Caches de 512 Kbytes a 8 MBYTE que son controladas con un bus distinto de la parte posterior de 72-bits: 64-bits + 8-bits para ECC (corrección de error). Para el sistema K7 utiliza un bus que ópticamente parezca justo como una ranura 1 (solt 1), pero contiene algo totalmente diferente al bus del Pentium II (GTL+), AMD licenció el protocolo del bus EV6 de la Alpha 21264 de Digital que trabaja actualmente con 64 Bits y 100MHz en ambos bordes del reloj (llamado así DDR : Tarifa de datos doble(Double Data Rate), que se asemeja realmente a 200MHz 'clásicos'). De esta manera el bus que AMD también llama ' S2K ' alcanza un índice de transferencia máximo de 1.6 GByte/s, dos veces más rápido que la competencia actual de Intel. Las últimas implementaciones deben trabajar con 133MHz y 200MHz e ir así hasta los 3.2 GByte/s.

5.2.3.- Tráfico del bus

El S2K es principalmente 'bus de explosión, burst bus'. Si los Direccionamientos no son secuenciales, se encuentra el problema de tener que poner junto el nuevo direccionamiento, lo que es absolutamente laborioso. De hecho el bus tiene solamente 13 canales de direccionamiento por dirección. El procesador necesita la dirección leer la dirección para chequear si un busmaster o un procesador diferente está teniendo acceso a una dirección que esté actualmente en la cache (el snooping).

Entre otras cosas esta restricción es un precio que hay que pagar por una ranura barata (las de AMD son la ranura A), con respecto a altas tarifas de datos de hasta 400MHz: Casi la mitad de los 242 pines de la ranura A(solt A) son utilizadas para el voltaje a tierra o de la base y no deja bastante espacio para los 64 canales de datos, 36 canales de direcciones y varios canales de control. La ranura 1 del Pentium III por otra parte utiliza solamente la cuarta parte de los canales para el voltaje a tierra.

K7 almacena hasta 72 ROPs decodificados temporalmente. Las nueve unidades (IEU: Número entero, AGU: Generación De Direcciones, FPU: El punto flotante) pueden trabajar en paralelo. La figura Nro. 5.2.c muestra este almacenamiento.

El diseño P6 del Pentium III almacena solamente 20 OPS temporales, que pueden ser distribuidos sobre cinco puertos. La Figura Nro. 5.2.d muestra este almacenamiento.

Fig. Nro. 5.2.c, Almacenamiento de ROPs del K7

Fig. Nro. 5.2.d Almacenamiento de OPs del Pentium III

Sin embargo, las explosiones (burts) son absolutamente comunes y en el PCI o AGP hay generalmente explosiones casi siempre más grandes, significando acceso a los Direccionamientos secuenciales. Los accesos a la memoria principal saltarán probablemente alrededor en el espacio de direccionamiento más frecuente pero las memorias dinámicas cuentan con que el direccionamiento esté dividido en dos porciones (RAS y CAS), así con un protocolo listo a dividir el direccionamiento en piezas más pequeñas no debe conducir a ningún retardo. En total el direccionamiento incluye 43Bits (8 Terabyte) y entra así más allá del mundo del Pentium de 36Bits.

5.2.4.- 3DNow! Desacelerado.

Cuando 3DNow! era introducido, faltaba una instrucción de intercambio para el programa de prueba patrón de Mandelbrodt que intercambia las dos mitades 32-bit: pero , aquí está: el PSWAPD. Se pudo Haber utilizado antes (pero en una forma diferente de PSWAPW) porque junto con dos instrucciones más fue parte del conjunto original de instrucciones 3DNow! (y es también parte del MASM 6,13). Desafortunadamente AMD fue forzado a sacrificar estas instrucciones, como tributo al acuerdo con Cyrix en el estándar común para 3DNow! (ese que Cyrix no ha puesto en ejecución hasta este día).

PSWAPD acelera el algoritmo fractal en un 20 por ciento (quizás AMD agregó esta instrucción solo para el programa de Mandelbrodt). Sin embargo, el programa de Mandelbrodt también reveló una debilidad del K7: En el mejor caso es posible poner dos instrucciones en ambas tuberías con cada ciclo del reloj pero el tiempo de espera de la mayoría de las instrucciones 3DNow! están con cuatro ciclos del reloj, dos veces más grandes que el K6-2/III. Y en el caso peor aún más tiempo de espera se agrega a este tiempo durante el acceso a la unidad de carga/almacenamiento. El K6-III es mejor en esto: en el mismo ciclo del reloj un K6-III tiene levemente mejor calidad de 3Dnow! que el K7, el cual no es capaz de aprovecharse de las nuevas instrucciones. Para el ahora programa Mandelbrodt 'manualmente optimizado' el K6-III solamente necesita 12 ciclos de reloj por la iteración.

En el protocolo EV6 cada procesador tiene un bus de Cache L2 en la parte posterior y su propio camino al chipset (de punto a punto). La Figura Nro. 5.2.e muestra este protocolo.

Fig. Nro. 5.2.e, Protocolo EV6 para el K7.

Intel promueve el Pentium III con la característica 'memoria que fluye, memory streaming' pero el K7 puede mantenerse: Ofrece un Buffer de 64 Kbytes y soporta todas las instrucciones del prefetch: cargando los datos que desvían a la cache L1 o a la cache L2.

Afortunadamente los llamados 'registros del rango del tipo de memoria' son compatibles con el Pentium II/III. Estos registros permiten accesos perceptiblemente más rápidos al Buffer intermediario de tarjetas gráficas. Los programadores de las tarjetas de los gráficos no necesitan subir a una solución especial, como lo tuvieron que hacer por ejemplo para el K6-2/III.

Como resumen se puede decir que sin una duda K7 no es solo la competencia ideal del Pentium III, su diseño tiene un enorme potencial para el futuro y mostrará sus capacidades verdaderas en 1 GHz y más. Por otra parte el diseño del Pentium II/III debe alcanzar lentamente un límite en 700 a 800MHz, aunque está seleccionado cuidadosamente, los ejemplos administrados ya manejan 1 GHz. Intel Necesita apresurarse y acabar el sucesor “Willamette”, AMD tendrá hasta entonces una ventaja de quizá un año. Si la compañía de Sunnyvale es capaz de utilizar esta ventaja unas pocas cosas podrán cambiar en el sector x86.

Como anexo se puede Irongate es el nombre del chipset que AMD envió como ayudante para el K7, contra la exhaustiva campaña en contra del Pentium III. Aparte del bus del procesador (protocolo EV6) que se asemeja a un chipset de Intel BX/GX: Un controlador del sistema (751) con el bus de memoria para PC100 DRAMs hasta 768 MBYTE y AGP 2,0 y un controlador periférico (756) que ofrece seis ranuras para PCI (todo el busmaster posible), ISA, USB y los periféricos usuales de los x86.

Hasta este momento, esta solamente el diseño IronGate de AMD, ese que ofrece además del sistema EV6, transporte para los periférico usuales de los x86.

La figura Nro. 5.2.f muestra este diseño.

Fig. Nro. 5.2.f, Diseño IronGate de AMD.

Aparentemente también se conforma con ACPI y PC98. El controlador del PCI está ya en nivel del PCI 2,2, significando apoyo para el busmaster de 64-bits y de 3.3 V también. Los buffers del PCI (cinco FIFOs con un total de 300 Bytes y de un buffer prefetch de 32 Bytes) permiten transferencias rápidas del PCI. Actualmente EV6 soporta Irongate con 100MHz de datos dobles(DDR), 133 MHz y 200MHz. El mapeo de direcciones entre el bus EV6 y los periféricos x86 son compatibles con el K7 y el Alpha. Para este caso el chipset maneja un vector gráfico de Remap de direcciones(GART) para asociar las tarjetas gráficas de AGP. Por lo tanto Irongate se puede también utilizar para los procesadores alpha, por ejemplo en la tarjeta UP1000 de API (Alpha Processor Inc.).

6.- CONCLUSIONES

Sin duda que los microprocesadores son y serán el “alma” de los computadores, ellos son quienes dan las ordenes a los demás periféricos, son sin duda la pieza más delicada y más costosa de los actuales computadores, desde sus inicios hasta nuestros días han tenido una serie de cambios, que los han llevado a ser cada día mas poderosos y satisfacer así las múltiples necesidades de sus millones de usuarios en el mundo, usuarios que no solo se remiten a tener un computador para uso domestico sino que también los utilizan para aplicaciones mas poderosas como servidores, controladores de sistemas, usos científicos, etc.

En el informe se pudo apreciar como han evolucionado las dos principales empresas del rubro, INTEL y AMD, esta ultima ha venido a opacar y a reducir el monopolio impuesto por Intel, sin duda que AMD ha sabido hacer las cosas, no es solo el hecho que sus procesadores son en forma general de mayor calidad que los de Intel, sino que también le ha dado un duro golpe a esta empresa en la parte que menos se lo esperaban, en los precios, ya que los procesadores de AMD son por lo general un 25% mas baratos que los de INTEL(comparados a un mismo nivel). Para uso domestico o de oficina un procesador AMD K6 II es mucho mas rápido y barato que un procesador INTEL Pentium II, en cualquier velocidad que se les compare, pero quizás la única ventaja que aun mantiene INTEL sobre AMD, aparte de los procesadores utilizados para servidores, donde los INTEL Pentium Pro son los mas indicados , sea en el prestigio, ya que por muy buenos y baratos que sean los AMD, siempre el común de la gente se va a inclinar por un INTEL, ese prestigio es el que espera ganarse algún día la empresa AMD, aunque con sus asociaciones con Microsoft entre otras empresas, de a poco va logrando hacerse de uno.

En resumen y a modo personal solo puedo acotar que en forma practica y solo para el uso de escritorio los procesadores AMD son verdaderamente muy superiores a los de INTEL, e incluso el nuevo super procesador de Intel, el Katmai o Pentium III ya ha sido derrotado por el Athlon o K7 de AMD, esto sin duda ha sido muy duro para Intel que ya esta pensando en su nuevo procesador, que en definitiva será una variación del actual Pentium III y que su nombre clave seria "Coppermine". A nivel de utilización como servidor no tengo antecedentes de las reales capacidades de los procesadores de AMD en comparación de los de INTEL, solo puedo agregar que el procesador ideal para este tipo de labor es el Pentium Pro y no el Pentium II como la misma INTEL trato de hacernos creer, pero este tipo de utilización al parecer sigue siendo explotada por INTEL, aunque nunca se sabe con AMD, quizás sus procesadores actuales ya pueden realizar estas actividades o en el futuro las realizaran, pero como he dicho, no poseo antecedentes al respecto.

Sin duda que AMD e INTEL son las empresas que dominan este rubro en el mundo, pero cabe señalar que hay una empresa que ha estado un poco en silencio, quizás preparando su arma secreta, pero sin duda es otra empresa de la cual hay que estar muy conscientes y no olvidarse de ella, me refiero, claro esta, a la empresa CYRIX que del anonimato puede pasar nuevamente a ser una de las grandes empresas desarrolladoras de microprocesadores, pero eso solo el tiempo lo dirá.

Quizás AMD pago su noviciado al ingresar al rubro con su procesador K5, el cual no fue todo lo bueno que se esperaba y paso lamentablemente sin pena ni gloria por el mercado mundial, de ahí en mas AMD se ha convertido en una pesadilla para INTEL y me atrevería a decir que el futuro se ve mas favorable para ellos que para cualquier otro competidor, llámese INTEL o CYRIX.

Evolución de los Microprocesadores (INTEL - AMD)

1

118

Descargar

| Enviado por: | El remitente no desea revelar su nombre |

| Idioma: | castellano |

| País: | España |